# Exploring the Feasibility of a DNA Computer: Design of an ALU using Sticker Based DNA Model

Mayukh Sarkar<sup>†</sup>, Prasun Ghosal<sup>†</sup>, Saraju P. Mohanty<sup>‡</sup> <sup>†</sup> Indian Institute of Engineering Science and Technology, Shibpur, Howrah 711103, WB, INDIA <sup>‡</sup> University of North Texas, Denton, TX 76203, USA email: {mayukh, p\_ghosal}@it.iiests.ac.in, saraju.mohanty@unt.edu

Abstract-Since its inception, DNA computing has advanced to offer an extremely powerful, energy-efficient emerging technology for solving hard computational problems with its inherent massive parallelism and extremely high data density. This would be much more powerful and general purpose when combined with other existing well known algorithmic solutions that exist for conventional computing architectures using a suitable ALU. Thus, a specifically designed DNA ALU that can address operations suitable for both domains can mitigate the gap between these two. A complete ALU (Arithmetic and Logic Unit) must be able to perform all possible logic operations including NOT, OR, AND, XOR, NOR, NAND and XNOR; compare, shift etc., integer and floating point arithmetic operations (Addition, Subtraction, Multiplication and Division). In this paper, design of a complete ALU has been proposed using Sticker-based DNA Model with experimental feasibility analysis. Novelties of this work may be in manifold. First, the integer arithmetic operations performed here are 2's complement arithmetic, and the floating point operations follow IEEE 754 floating point format, resembling closely to a conventional ALU. Also, the output of each operation can be reused for any next operation. So any algorithm or program logic that users can think of can be implemented directly on the DNA computer without any modification. Second, once the basic operations of sticker model can be automated, the implementations proposed in this work become highly suitable to design a fully automated complete ALU. Third, proposed approaches are easy to implement. Finally, these approaches can work on sufficiently large binary numbers.

Index Terms-DNA Computing, DNA ALU, Sticker Model.

## I. INTRODUCTION

IN recent years, computing using DNA molecules, namely, DNA computing, has been proved to be a powerful emerging technology to solve hard computational problem. In 1994, Adleman [1] has shown the use of this powerful tool in solving Travelling Salesman problem, a difficult combinatorial search problem. In 1995, Lipton [2], in a very similar way, solved the SAT problem, by representing all possible combination of values in a graph. Lipton's DNA algorithm for solving the SAT problem was a linear one, which is impossible for a conventional computer at this stage. In the same year, Boneh et.al. [3] broke DES, a famous encryption method, using DNA. In 1997, Ouyang et. al. [4] solved maximal clique problem given a six vertex graph. A huge achievement was made by Adleman and others in 2002, when they solved 20-variable 3-SAT problem by performing an exhaustive search over 1 million possibilities [5]. Along with these experiments, several other NP-complete problems, such as Graph Coloring [6], Bin Packing [7] etc. have been solved using DNA computing. All these experiments have shown that, inherently massive parallelism and high data storage density have made DNA computing a powerful technique to solve such problems over conventional computer. Though these works used massive amounts of data to be encoded on huge number of distinct DNA strands and each bio-molecular operation applied on a DNA solution affects all strands simultaneously leading to possibility of massive parallelism, but the proposed work in this paper looks at a different problem other than searching over a large search space. In fact, the problem targeted in the proposed work is to perform arithmetic and logic operations so that output of one operation can be used in later operations and this requires two numbers to be encoded by two different DNA strands in two separate test tubes. Hence power of massive parallelism is not visible in this work, as the target of this work is not to utilize existing power of DNA computer to solve another computationally hard problem. Rather it is to increase the power of the computing technique by showing that DNA computer can also be used effectively in arithmetic and logic operations and hence solving general problems that do not require search over large search spaces.

1

## A. Basics of DNA

The DNA (Deoxyribonucleic acid), naturally found in living cells, is composed of four bases, namely Adenine(A), Guanine(G), Thymine(T) and Cytosine(C). Each base is attached to its neighbour base in the sequence via phosphate bonding. Base, sugar and the phosphate are together called a nucleotide. Two DNA sequences bond with each other via hydrogen bonding between each Watson-Crick complementary base pairs (A with T, and C with G), forming DNA double helix. Each DNA strand has two ends : 5'-end and 3'-end, that determine the polarity of the DNA strand. During the formation of DNA double strand, two complementary single strands bond with each other in anti-parallel fashion.

## B. Recent Trends and Challenges

In 2002, a programmable molecular computing machine composed of enzymes and DNA molecules, have been developed by a group of researchers from Weizmann Institute of Science, Israel. A year later, the team advanced one step further. In the new device, the single DNA molecule, that provides the computer with the input data also provides all the necessary fuel [8]. In 2004, Benenson et. al. [9] described an autonomous bio-molecular computer that logically analyses the levels of messenger RNA species, and in response produces a molecule capable of affecting levels of gene expression. This computer, in theory, would be capable of diagnosing cancer, and producing anti-cancer drug. In 2013, Goldman et. al. [10] encoded computer files totaling 739 kB of hard disk storage and with an estimated Shannon information of  $5.2 \times 10^6$  bits into a DNA code, synthesized, sequenced and then reconstructed the original data with 100% accuracy. In the same year, bio-engineers at Stanford University created the first biological transistors, named transcriptor, using DNA and RNA [11].

## C. Necessity of a DNA ALU

To make DNA computing applicable on wider range of problems, simple logic and arithmetic operations available on a conventional computers, are necessary to be implemented. These operations include logic operations including NOT, OR, AND, XOR, NOR, NAND, and XNOR; compare, shift etc., integer and floating point arithmetic operations (Addition, Subtraction, Multiplication and Division). Proper and efficient implementations of these operations will allow the users to implement their algorithms and program logic directly on a DNA computer without any modification, thus making the applicability of the DNA computing technique in a much wider range.

## D. Organization of the paper

Rest of the paper is organized as follows. In section II, advantages of the proposed work are described with an explanation over how the proposed work fits into the automation of a future DNA computer. Section III reports the works that have been done in the field of arithmetic and logic operation implementations using DNA molecules, and the problems they pose. Section IV describes the background information necessary to understand the proposed work viz. the Stickerbased model, biomolecular operations available on the stickerbased DNA model, and their functional formulation. Seven primary logic operations viz. AND, OR, XOR, NAND, NOR, XNOR and NOT, are described in section V with an example demonstrating step-by-step execution of AND operation. Section VI describes the possible integer arithmetic operations viz. comparator, left and right shifters (logical, arithmetic and circular), addition / subtraction, multiplication, and division. Representation of IEEE 754 floating point format and arithmetic operations possible on the floating point numbers viz. addition / subtraction, multiplication, and division are presented in section VII. Following section VIII addresses the possibility of the implementations of the proposed work, complexity analysis, and implementation issues. Finally, section IX concludes the paper with possible future directions.

## II. NOVEL CONTRIBUTIONS OF THIS PAPER

DNA Computing is already proven powerful for computationally "hard" problems. Inherent parallelism nature of biomolecular operations gives this power to DNA computing. This would be much more powerful and general purpose when combined with other existing well known algorithmic solutions that exist for conventional computing architectures using a suitable ALU. Thus, a specifically designed DNA ALU that can address operations suitable for both domains can mitigate the gap between these two.

The novelties of the proposed method as well as the logic and arithmetic operations for this DNA ALU proposed in this work may be summarized as follows.

- Ease of number representation: Implementations are based on sticker based DNA model, and hence can explore the power of the binary number representation.

- Ease of implementations: Operations applicable on sticker-based DNA model are simple to implement, except the *clear* operation. Proposed operations avoid the *clear* operation of sticker model, and are using the simple operations, and hence physical implementation is easier.

- Input and output of the operations are of similar structure: The input operands are being taken as separate strands in separate test tubes, and output is also provided in separate test tube. Hence, the output of one operation can be used ready-made for any next operation, without any modification. Also, the uniform representation can be used, *i.e.*, the way an user needs to represent the input, the output can be decoded in the user-readable format in the similar manner without any modification.

- **Possibility of automation of DNA computer:** If the basic operations of sticker model, i.e. *combine*, *separate* and *set* can be automated, the proposed implementations are highly suitable for the design of a fully automated complete ALU.

- Design of a complete DNA ALU: All logic operations, integer, and floating point arithmetic operations have been implemented. Also all representations follow conventional ideology, such as floating point operations follow IEEE 754 floating point format and so on. So any algorithm or program logic that users can perform can be implemented directly on the DNA computer without any modification.

## **III. RELATED PRIOR RESEARCH**

The earliest attempt to perform arithmetic operations (addition of two binary numbers) using DNA was made by Guarneiri et.al. [12], but the output strands are vastly different from the input ones, and hence, cannot be reused for any next operation.

Later, Gupta et. al. [13] performed logic and arithmetic operations using fixed bit encoding scheme, but requires manual encoding and addition of intermediate results one by one during processing of arithmetic operations. This is time consuming task, and cannot be used in an automated DNA computer.

Santis et. al. [14] proposed floating-point arithmetic and logic operations using DNA strands, but it requires long DNA strand to represent a single bit, and representation of single binary number requires multiple test tubes. Bits toward LSB in long numbers requires much longer strands to represent.

Several other approaches for implementing arithmetic and logic operations have been proposed, such as Ogihara-Ray method of boolean circuit simulation [15], Amos-Dunne method [16], Barua-Misra method [17], Qiu-Lu method [18] etc.. But none of them are based on sticker based DNA model.

Ignatova et. al. [19] have considered many sticker algorithms, including some simple arithmetic. Guo et. al. [20] proposed an implementation of arithmetic operations using sticker-based DNA model, but they did not propose logic operations and floating point operations. The two numbers under operation, along with the carry are being represented on same memory strand, and output of operation are found as a substring of the output strand. So, the output of one operation can not be reused for next one, until and unless, the remaining parts of the output strand is cleared, and next operand is set at that position. Also, they have used *clear* operation, but as Roweis et. al. [21] have specified in the base paper of Stickerbased DNA Model , "In terms of physical implementation prospects, *clear* seems to be the most problematic of our operations".

Arnold [22], [23] proposed a more efficient sticker addition algorithm, known as tube-encoded carry; however, this operates in a similar context of [19] and [20] where both operands are represented on the same strand. The major advantage of [22] is that carries are not recorded on DNA strands, rather represented by the tube the strands are placed in. This algorithm is adapted here to make an efficient addition/subtraction algorithm in the different context where two numbers on two distinct strands of DNA produce a sum on a third strand that may be reused in later operations.

Therefore, it remains a challenging task to have all the logic and arithmetic operations implemented with same input and output DNA format, practically possible and easy to implement.

## IV. BACKGROUND OF DNA COMPUTER

## A. Sticker-based Model

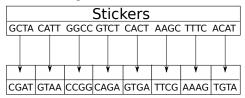

A binary number can be represented in the DNA sticker model by employing two groups of single-stranded DNA molecules. One is *memory strand*, which is a long DNA molecule, subdivided into several non-overlapping region. The other group is a set of *stickers*, which are short DNA molecules, each having length equal to the length of each region of memory strand. Each sticker is complementary to one and only one of the non-overlapping regions. Each nonoverlapping region represents a bit. If a sticker is annealed to its matching region on the memory strand, that region then represents 1 bit, otherwise a 0 bit. For example, to represent a 8-bit number, if we take the memory strand and the corresponding stickers as in Figure 1, where each sticker is complementary to each of the 8 nonoverlapping regions respectively. As an example, the numbers 10101110 and 11011001 can be represented using the above sticker model as in Figure 2.

Fig. 1: An example memory strand with corresponding stickers

| GCTA |      | GGCC |      | CACT | AAGC | тпс  |      |

|------|------|------|------|------|------|------|------|

| CGAT | GTAA | CCGG | CAGA | GTGA | TTCG | AAAG | TGTA |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0    |

|      |      |      |      |      |      |      |      |

| GCTA | CATT |      | GTCT | CACT |      |      | ACAT |

| CGAT | GTAA | CCGG | CAGA | GTGA | TTCG | AAAG | TGTA |

| 1    | 1    | •    | 1    | -    | •    | •    | 1    |

Fig. 2: An example memory strand with corresponding stickers

Any set of bit strings can be represented by identical memory strands, each memory strand having stickers annealed only at the required 1 bit positions.

### B. Operations on Sticker based DNA

The operations available on sticker-based DNA strands are as follows.

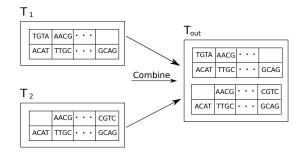

- Combine : In this operation, two sets of bit strings in two test tubes in combined in one test tube. This corresponds to obtaining a different tube containing all the memory complexes from both input tubes. The combine operation is not the same as a conventional assignment statement: combine moves DNA strands to a different physical location whereas conventional assignment makes a copy.

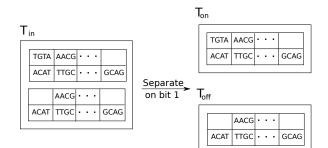

- Separate : In this operation, a set of strings is separated into two sets based on a particular bit. This creates two different tubes, where one tube contains strings having that particular bit *on*, and the other tube containing the strings having the bit *off*.

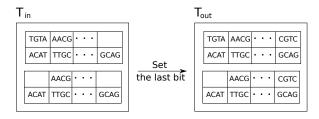

- 3) *Set* : In this operation, a particular bit in every string of the DNA solution is set (turned on). The sticker

Fig. 3: Combine operation

Fig. 4: Separate operation

Fig. 5: Set operation

for that bit is annealed to the appropriate region on every complex in the set's tube. Setting is performed by annealing the particular sticker to the bit that needs to be set in the memory strand. Setting multiple bits can be done in parallel by pouring all the stickers corresponding to the targeted bits, and annealing. All the poured stickers will anneal with the memory strand at the same time. Excess stickers need to be filtered out of the tube before proceeding to the next operation.

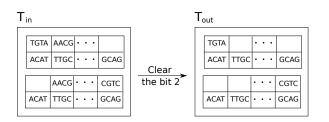

- 4) Clear : In this operation, a particular bit in every string of a DNA solution, is removed by removing the sticker (if present) for that bit from every memory complexes in the test tube. Implementation of this operation is difficult, and hence avoided in the proposed algorithms.

- 5) *Discard* : In this operation, contents of a non-empty test tube is discarded and the test tube becomes empty after this operation.

## C. Functional formulation of the operations available on Sticker-based DNA model

For the ease of representation, functional formulations of the operations described in the previous subsection IV-B will be used as follows.

1)  $Combine(T_{dest}; T_{src}^1, T_{src}^2, \cdots, T_{src}^n)$  - Pour the contents of  $T_{src}$ s in  $T_{dest}$ . After this operation,  $T_{dest}$  will

Fig. 6: Clear operation

contain the union of the contents of  $T_{dest}$  and all the  $T_{src}$ s, and  $T_{src}$ s will become empty.

- 2)  $Separate(T_1, i, b_{on}, b_{off})$  Separate the contents of  $T_1$  based on the value of  $i^{th}$  bit in two test tubes  $b_{on}$ , containing DNA strands having  $i^{th}$  bit on, and  $b_{off}$ , containing DNA strands having  $i^{th}$  bit off.

- 3)  $Set(T_1, i)$  Set the  $i^{th}$  bit  $b_i$  of all DNA strand in test tube  $T_1$ .

- 4) Discard(T) Discard the contents of test tube T.

## V. PROPOSED APPROACHES FOR LOGIC OPERATIONS USING DNA

All possible logic operations, *viz.*, AND, OR, XOR, NAND, NOR, XNOR, NOT are being proposed in this section. But before describing the operations to be performed in the proposed ALU, a helper operation *Substring* needs to be discussed, that will help in making backup of input test tubes and will allow the input test tubes to stay intact, so that they can be used in other operations without recreating the numbers.

## A. Substring

Substring operation takes a *n*-bit input string in a test tube  $T_{in}$ , a start index *start* and an end index *end*, such that  $0 \leq start \leq end < n$ . The operation will output the required DNA strand in test tube  $T_{out}$  that will represent the substring of the input string from start index to end index, taking end index inclusive. This operation itself may not be used as a part of main ALU operations, but will be proved helpful in several of next operations. The value of *n* will be specified in later algorithms that use substring and is global for all routines that use Algorithm 1. Typical choices for *n* are 16, 32 and 64 for integers and 22, 46 and 108 for floating point (twice the mantissa size).

## Algorithm 1 Sub string

| 1: <b>procedure</b> SUBSTRING( $in : T_{in}, start, end; out : T_{out}$ )   |  |  |

|-----------------------------------------------------------------------------|--|--|

| 2: $length \leftarrow end - start + 1;$                                     |  |  |

| 3: Pour blank memory strands of <i>length</i> bits, $0000$ , in $T_{out}$ ; |  |  |

| length bits                                                                 |  |  |

| 4: for $i \leftarrow 0$ to $length - 1$ do                                  |  |  |

| 5: Separate $(T_{in}, start + i, b_{on}, b_{off})$ ;                        |  |  |

| 6: <b>if</b> $\hat{b}_{on}$ is not empty <b>then</b>                        |  |  |

| 7: $\operatorname{Set}(T_{out}, i);$                                        |  |  |

| 8: end if                                                                   |  |  |

| 9: Combine $(T_{in}; b_{on}, b_{off});$                                     |  |  |

| 10: end for                                                                 |  |  |

| 11: end procedure                                                           |  |  |

Now, the logic operations can be discussed. Let two test tubes  $T_1$  and  $T_2$  be containing the DNA strands corresponding to the two *n*-bit binary numbers under operation, respectively. The test tube  $T_{out}$  will contain the output after the corresponding operation. At the beginning of each operation,  $T_{out}$  is considered to contain blank memory strands, *i.e.*, the string 00...00.

n bits The implementations of the logic operations as follows,

Fig. 7: DNA molecules for the example of AND operation

## B. AND Operation

Algorithm 2 performs AND operation between two *n*-bit numbers represented using sticker model, and kept in two test tubes  $T_1$  and  $T_2$  respectively. The output of the operation is available in test tube  $T_{out}$ , also in sticker model representation. This algorithm checks whether both numbers have value of 1 at each bit, and runs in O(n) time.

## Algorithm 2 AND Logic

| 1: procedure AND $(in : T_1, T_2, n; out : T_{out})$                                           |  |  |  |

|------------------------------------------------------------------------------------------------|--|--|--|

| 2: $T_1^C \leftarrow Substring(T_1, 0, n-1);$<br>3: $T_2^C \leftarrow Substring(T_2, 0, n-1);$ |  |  |  |

| 3: $T_2^C \leftarrow Substring(T_2, 0, n-1);$                                                  |  |  |  |

| 4: Pour blank memory strands of <i>n</i> bits, $00 \dots 00$ , in $T_{out}$ ;                  |  |  |  |

| <i>n</i> bits                                                                                  |  |  |  |

| 5: Combine $(T_C; T_1^C, T_2^C);$                                                              |  |  |  |

| 6: for all bit $i$ do                                                                          |  |  |  |

| 7: Separate $(T_C, i, b_{on}, b_{off})$ ;                                                      |  |  |  |

| 8: <b>if</b> $b_{off}$ is empty <b>then</b>                                                    |  |  |  |

| $\triangleright i^{th}$ bits of both numbers are 1                                             |  |  |  |

| 9: $\operatorname{Set}(T_{out}, i);$                                                           |  |  |  |

| 10: end if                                                                                     |  |  |  |

| 11: Combine $(T_C; b_{on}, b_{off});$                                                          |  |  |  |

| 12: end for                                                                                    |  |  |  |

| 13: end procedure                                                                              |  |  |  |

| 1                                                                                              |  |  |  |

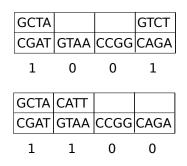

As an example, assume two 4-bit numbers, 1001 and 1100 be kept in two test tubes  $T_1$  and  $T_2$  respectively. Let the memory strand be CGAT|GTAA|CCGG|CAGA. Hence, the two numbers will be represented as in Figure 7.

Now, the algorithm runs as follows.

- 1) The contents of  $T_1$  and  $T_2$  are first taken as a backup into  $T_1^C$  and  $T_2^C$  respectively and combined into  $T_C$ . Hence,  $T_C$  now contains {1001, 1100}. Blank memory strands are taken into test tube  $T_{out}$ .

- 2)  $T_C$  is separated based on bit 1,  $b_{on}$  contains both 1001 and 1100, and  $b_{off}$  is empty. So, the sticker for bit 1, GTTA is taken into test tube  $T_{out}$ , and annealed to set bit 1 of output.

- 3)  $T_C$  is separated based on bit 2,  $b_{on}$  contains 1100, and  $b_{off}$  contains 1001. As  $b_{off}$  is not empty, nothing to do. Combine  $b_{on}$  and  $b_{off}$  back into  $T_C$ .

- 4)  $T_C$  is separated based on bit 3,  $b_{on}$  is empty, and  $b_{off}$  contains both 1001 and 1100. As  $b_{off}$  is not empty, nothing to do. Combine  $b_{on}$  and  $b_{off}$  back into  $T_C$ .

- 5)  $T_C$  is separated based on bit 4,  $b_{on}$  contains 1001, and  $b_{off}$  contains 1100. As  $b_{off}$  is not empty, nothing to do. Combine  $b_{on}$  and  $b_{off}$  back into  $T_C$ .

- 6)  $T_{out}$  now contains the DNA strand as in Figure 8, representing the value 1000.

| GCTA |      |      |      |

|------|------|------|------|

| CGAT | GTAA | CCGG | CAGA |

| 1    | 0    | 0    | 0    |

Fig. 8: DNA molecule representing output of AND operation

## C. OR Operation

Algorithm 3 performs OR operation between two *n*-bit numbers kept in two test tubes  $T_1$  and  $T_2$  respectively. The output of the operation is available in test tube  $T_{out}$ . Following the similar logic of AND operation, as it checks for each bit whether atleast one of them is 1, this algorithm also takes O(n) number of steps to perform.

## Algorithm 3 OR Logic

| 1: procedure $OR(in : T_1, T_2, n; out : T_{out})$                     |  |  |  |

|------------------------------------------------------------------------|--|--|--|

| 2: $T_1^C \leftarrow Substring(T_1, 0, n-1);$                          |  |  |  |

| 3: $T_2^C \leftarrow Substring(T_2, 0, n-1);$                          |  |  |  |

| 4: Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ; |  |  |  |

| <i>n</i> bits                                                          |  |  |  |

| 5: Combine $(T_C; T_1^C, T_2^C);$                                      |  |  |  |

| 6: for all bit <i>i</i> do                                             |  |  |  |

| 7: Separate $(T_C, i, b_{on}, b_{off})$ ;                              |  |  |  |

| 8: <b>if</b> $b_{on}$ is not empty <b>then</b>                         |  |  |  |

| $\triangleright i^{th}$ bit of atleast one number is 1                 |  |  |  |

| 9: $\operatorname{Set}(T_{out}, i);$                                   |  |  |  |

| 10: end if                                                             |  |  |  |

| 11: Combine $(T_C; b_{on}, b_{off});$                                  |  |  |  |

| 12: end for                                                            |  |  |  |

| 13: end procedure                                                      |  |  |  |

## D. XOR Operation

Algorithm 4 performs XOR operation between two *n*-bit numbers kept in two test tubes  $T_1$  and  $T_2$  respectively. The output of the operation is available in test tube  $T_{out}$ . This algorithm is also O(n), as it is checking whether the bits of the two input numbers are different for each bit.

## Algorithm 4 XOR Logic

| 1: procedure $XOR(in : T_1, T_2, n; out : T_{out})$                    |

|------------------------------------------------------------------------|

| 2: $T_1^C \leftarrow Substring(T_1, 0, n-1);$                          |

| 3: $T_2^C \leftarrow Substring(T_2, 0, n-1);$                          |

| 4: Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ; |

| <i>n</i> bits                                                          |

| 5: Combine $(T_C; T_1^C, T_2^C)$ ;                                     |

| 6: for all bit <i>i</i> do                                             |

| 7: Separate $(T_C, i, b_{on}, b_{off})$ ;                              |

| 8: <b>if</b> neither $b_{on}$ nor $b_{off}$ is empty <b>then</b>       |

| $\triangleright i^{th}$ bits of two numbers are different              |

| 9: $\operatorname{Set}(T_{out}, i);$                                   |

| 10: end if                                                             |

| 11: Combine $(T_C; b_{on}, b_{off});$                                  |

| 12: end for                                                            |

| 13: end procedure                                                      |

## E. NAND Operation

Algorithm 5 performs NAND operation between two *n*-bit numbers kept in two test tubes  $T_1$  and  $T_2$  respectively. The output of the operation is available in test tube  $T_{out}$ . This algorithm runs in O(n) number of steps.

## Algorithm 5 NAND Logic

1: procedure NAND $(in : T_1, T_2, n; out : T_{out})$  $T_1^C \leftarrow Substring(T_1, \circ, T_2^C \leftarrow Substring(T_2, 0, n-1);$ 2: 3: 4: Pour blank memory strands of *n* bits, 00...00, in  $T_{out}$ ; Combine $(T_C; T_1^C, T_2^C);$ 5: for all bit i do 6: Separate $(T_C, i, b_{on}, b_{off})$ ; 7: 8: if  $\bar{b}_{off}$  is not empty then  $\triangleright i^{th}$  bit of atleast one number is 0 9:  $Set(T_{out}, i);$ 10: end if 11:  $Combine(T_C; b_{on}, b_{off});$ end for 12: 13: end procedure

## F. NOR Operation

Algorithm 6 performs NOR operation between two *n*-bit numbers kept in two test tubes  $T_1$  and  $T_2$  respectively. The output of the operation is available in test tube  $T_{out}$ . Similar to other logic operations, this is O(n) time.

#### Algorithm 6 NOR Logic

| 1: procedure NOR( $in: T_1, T_2, n; out: T_{out}$ )                                      |  |  |  |

|------------------------------------------------------------------------------------------|--|--|--|

| : $T_1^C \leftarrow Substring(T_1, 0, n-1);$                                             |  |  |  |

| $T_1^C \leftarrow Substring(T_1, 0, n-1);$<br>$T_2^C \leftarrow Substring(T_2, 0, n-1);$ |  |  |  |

| 4: Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ;                   |  |  |  |

| <i>n</i> bits                                                                            |  |  |  |

| 5: Combine $(T_C; T_1^C, T_2^C);$                                                        |  |  |  |

| 6: for all bit $i$ do                                                                    |  |  |  |

| 7: Separate $(T_C, i, b_{on}, b_{off})$ ;                                                |  |  |  |

| 8: <b>if</b> $b_{on}$ is empty <b>then</b>                                               |  |  |  |

| $\triangleright i^{th}$ bits of both numbers are                                         |  |  |  |

| 9: $\operatorname{Set}(T_{out}, i);$                                                     |  |  |  |

| 10: end if                                                                               |  |  |  |

| 11: Combine $(T_C; b_{on}, b_{off});$                                                    |  |  |  |

| 12: end for                                                                              |  |  |  |

| 13: end procedure                                                                        |  |  |  |

#### G. XNOR Operation

Algorithm 7 performs XNOR operation between two *n*-bit numbers kept in two test tubes  $T_1$  and  $T_2$  respectively. The output of the operation is available in test tube  $T_{out}$ . This algorithm also has O(n) number of steps.

## Algorithm 7 XNOR Logic

| 1: procedure $XNOR(in : T_1, T_2, n; out : T_{out})$                                           |  |  |

|------------------------------------------------------------------------------------------------|--|--|

| 2: $T_1^C \leftarrow Substring(T_1, 0, n-1);$                                                  |  |  |

| 2: $T_1^C \leftarrow Substring(T_1, 0, n-1);$<br>3: $T_2^C \leftarrow Substring(T_2, 0, n-1);$ |  |  |

| 4: Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ;                         |  |  |

| <i>n</i> bits                                                                                  |  |  |

| 5: Combine $(T_C; T_1^C, T_2^C)$ ;                                                             |  |  |

| 6: <b>for all</b> bit $i$ <b>do</b>                                                            |  |  |

| 7: Separate $(T_C, i, b_{on}, b_{off})$ ;                                                      |  |  |

| 8: <b>if</b> either $b_{on}$ or $b_{off}$ is empty <b>then</b>                                 |  |  |

| $\triangleright i^{th}$ bits of two numbers are same                                           |  |  |

| 9: $\operatorname{Set}(T_{out}, i);$                                                           |  |  |

| 10: end if                                                                                     |  |  |

| 11: Combine $(T_C; b_{on}, b_{off});$                                                          |  |  |

| 12: end for                                                                                    |  |  |

| 13: end procedure                                                                              |  |  |

|                                                                                                |  |  |

## H. NOT Operation

Algorithm 8 performs NOT of a *n*-bit number kept in the test tube  $T_1$ . The output of the operation is available in test tube  $T_{out}$ . This algorithm checks for the value of each bit, ine by one, of the input number too and hence has O(n) number of steps.

#### Algorithm 8 NOT Logic

|       | -                                                                   |  |  |  |

|-------|---------------------------------------------------------------------|--|--|--|

| 1: p  | 1: procedure NOT( $in : T_{in}, n; out : T_{out}$ )                 |  |  |  |

| 2:    | Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ; |  |  |  |

|       | <i>n</i> bits                                                       |  |  |  |

| 3:    | for all bit i do                                                    |  |  |  |

| 4:    | Separate $(T_{in}, i, b_{on}, b_{off})$ ;                           |  |  |  |

| 5:    | if $\hat{b}_{on}$ is empty then                                     |  |  |  |

|       | $\triangleright i^{th}$ bit is 0                                    |  |  |  |

| 6:    | $\operatorname{Set}(T_{out}, i);$                                   |  |  |  |

| 7:    | end if                                                              |  |  |  |

| 8:    | $Combine(T_{in}; b_{on}, b_{off});$                                 |  |  |  |

| 9:    | end for                                                             |  |  |  |

| 10: e | 10: end procedure                                                   |  |  |  |

|       | -                                                                   |  |  |  |

## VI. PROPOSED APPROACHES FOR INTEGER ARITHMETIC OPERATIONS USING DNA

In the following operations, two numbers under operation will be considered of n bits each, and will be kept in two separate test tubes initially. Assume, test tube  $T_1$  containing the number  $a_0a_1 \cdots a_{n-2}a_{n-1}$ , and test tube  $T_2$  containing the number  $c_0c_1 \cdots c_{n-2}c_{n-1}$ . If the two numbers are of unequal bit count, smaller number will be appended with 0 bits on the left side to make them equal length. For both of the numbers, index 0 will represent the MSB, and index n-1 will represent the LSB. This is often called Big-Endian Order.

## A. Comparator

The comparator operation 9 will compare two *n*-bit numbers in  $T_1$  and  $T_2$ , and store the result in three test tubes  $T_g$ ,  $T_l$ and  $T_e$ , initially empty. If unequal,  $T_g$  will contain the greater number,  $T_l$  will contain the smaller number, and  $T_e$  will remain empty. If the two numbers are equal,  $T_e$  will contain both of the numbers, and the rest of the two test tubes will remain empty. This algorithm runs in O(n) number of steps.

## Algorithm 9 Comparator

| 1:  | <b>procedure</b> COMPARATOR $(in : T_1, T_2, n; out : T_g, T_l, T_e)$ |

|-----|-----------------------------------------------------------------------|

| 2:  | $T_1^C \leftarrow Substring(T_1, 0, n-1);$                            |

| 3:  | $T_2^C \leftarrow Substring(T_2, 0, n-1);$                            |

| 4:  | $\tilde{\text{Combine}}(T_C; T_1^C, T_2^C);$                          |

| 5:  | for all bit i from MSB to LSB do                                      |

| 6:  | Separate $(T_C, i, b_{on}, b_{off});$                                 |

| 7:  | if $b_{on}$ or $b_{off}$ is empty then                                |

| 8:  | $Combine(T_C; b_{on}, b_{off});$                                      |

| 9:  | else                                                                  |

| 10: | $Combine(T_g; b_{on});$                                               |

| 11: | Combine $(T_l; b_{off});$                                             |

| 12: | break ▷ Exit from for loop                                            |

| 13: | end if                                                                |

| 14: | end for                                                               |

| 15: | if both $T_g$ and $T_l$ are empty then                                |

|     | $\triangleright T_C$ contains both strands                            |

| 16: | $Combine(T_e; T_C);$                                                  |

| 17: | end if                                                                |

| 18: | end procedure                                                         |

## B. Left Shifter and Right Shifter

The Left Shifter (Right Shifter) operations will take a single *n*-bit number in  $T_{in}$  test tube as input, left shift (right shift) the number by one bit, and output the shifted number in test tube  $T_{out}$ .  $T_{out}$  initially contains blank memory strands, i.e., the number 0000...0, no stickers are annealed to the memory strands. All types of shifters (Logical, Arithmetic and Circular) in both directions, except arithmetic left shift, are presented below, as arithmetic left shift and logical left shift are similar in nature. All of these shifters will complete in O(n) time.

1) Logical Left Shift: In logical left shift, all the bits except the left most bit (MSB) is shifted to the left, and the MSB is discarded. Algorithm 10 performs the logical left shift of n-bit number kept in test tube  $T_{in}$  and outputs the result in test tube  $T_{out}$ .

| Algorithm 10 Logical Left Shifter                                      |                                                                         |                                                |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------|--|--|

| 1: p                                                                   | 1: <b>procedure</b> LOGICALLEFTSHIFT( $in : T_{in}, n; out : T_{out}$ ) |                                                |  |  |

| 2: Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ; |                                                                         |                                                |  |  |

|                                                                        |                                                                         | n bits                                         |  |  |

| 3:                                                                     | for all bit i except MSB do                                             | $\triangleright$ Leave $0^{th}$ bit            |  |  |

| 4:                                                                     | Separate $(T_{in}, i, b_{on}, b_{off})$ ;                               |                                                |  |  |

| 5:                                                                     | if $b_{on}$ is not empty then                                           | $\triangleright i^{th}$ bit of the number is 1 |  |  |

| 6:                                                                     | $Set(T_{out}, i-1);$                                                    |                                                |  |  |

| 7:                                                                     | end if                                                                  |                                                |  |  |

| 8:                                                                     | Combine $(T_{in}; b_{on}, b_{off});$                                    |                                                |  |  |

| 9:                                                                     | 9: end for                                                              |                                                |  |  |

| 10: <b>e</b>                                                           | 10: end procedure                                                       |                                                |  |  |

2) Logical Right Shift: In logical right shift, all the bits except the right most bit (LSB) is shifted to the right, and the LSB is discarded. Algorithm 11 performs the logical right shift of *n*-bit number kept in test tube  $T_{in}$  and outputs the result in test tube  $T_{out}$ .

#### Algorithm 11 Logical Right Shifter

| 1: procedure LOGICALRIGHTSHIFT( $in : T_{in}, n; out : T_{out}$ )      |                                                |  |  |

|------------------------------------------------------------------------|------------------------------------------------|--|--|

| 2: Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ; |                                                |  |  |

|                                                                        | <i>n</i> bits                                  |  |  |

| 3: for all bit <i>i</i> except LSB do                                  | $\triangleright$ Leave $n - 1^{th}$ bit        |  |  |

| 4: Separate $(T_{in}, i, b_{on}, b_{off})$ ;                           |                                                |  |  |

| 5: <b>if</b> $b_{on}$ is not empty <b>then</b>                         | $\triangleright i^{th}$ bit of the number is 1 |  |  |

| 6: $Set(T_{out}, i+1);$                                                |                                                |  |  |

| 7: end if                                                              |                                                |  |  |

| 8: Combine $(T_{in}; b_{on}, b_{off});$                                |                                                |  |  |

| 9: end for                                                             |                                                |  |  |

| 10: end procedure                                                      |                                                |  |  |

|                                                                        |                                                |  |  |

3) Arithmetic Right Shift: In arithmetic right shift, all the bits except the right most bit (LSB) is shifted to the right, the LSB is discarded, and the sign bit (MSB) is preserved. Algorithm 12 performs the arithmetic right shift of n-bit number kept in test tube  $T_{in}$  and outputs the result in test tube  $T_{out}$ .

#### Algorithm 12 Arithmetic Right Shifter

| 1:  | 1: procedure ARITHMETICRIGHTSHIFT $(in : T_{in}, n; out : T_{out})$ |                                             |  |

|-----|---------------------------------------------------------------------|---------------------------------------------|--|

| 2:  | Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ; |                                             |  |

|     |                                                                     | <i>n</i> bits                               |  |

| 3:  | for all bit i except LSB do                                         | $\triangleright$ Leave $n - 1^{th}$ bit     |  |

| 4:  | Separate $(T_{in}, i, b_{on}, b_{off});$                            |                                             |  |

| 5:  | if $b_{on}$ is not empty then                                       | $\triangleright i^{th}$ of the number is 1  |  |

| 6:  | if $i = 0$ then                                                     | $\triangleright$ MSB is 1, preserve the MSB |  |

| 7:  | $\operatorname{Set}(T_{out}, 0);$                                   |                                             |  |

| 8:  | end if                                                              |                                             |  |

| 9:  | $\operatorname{Set}(T_{out}, i+1);$                                 |                                             |  |

| 10: | end if                                                              |                                             |  |

| 11: | $Combine(T_{in}; b_{on}, b_{off});$                                 |                                             |  |

| 12: | end for                                                             |                                             |  |

| 13: | end procedure                                                       |                                             |  |

4) Circular Left Shift: In circular left shift, all the bits except the left most bit (MSB) is shifted to the left, and the MSB is circulated to LSB. Algorithm 13 performs the circular left shift of *n*-bit number kept in test tube  $T_{in}$  and outputs the result in test tube  $T_{out}$ .

Algorithm 13 Circular Left Shifter

| 1: <b>procedure</b> CIRCULARLEFTSHIFT $(in : T_{in}, n; out : T_{out})$<br>2: Pour blank memory strands of <i>n</i> bits, 0000, in $T_{out}$ ; |                                                |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|

|                                                                                                                                                | <i>n</i> bits                                  |  |

| 3: for all bit <i>i</i> do                                                                                                                     |                                                |  |

| 4: Separate $(T_{in}, i, b_{on}, b_{off})$ ;                                                                                                   |                                                |  |

| 5: <b>if</b> $b_{on}$ is not empty <b>then</b>                                                                                                 | $\triangleright i^{th}$ bit of the number is 1 |  |

| 6: <b>if</b> $i = 0$ then                                                                                                                      | ▷ MSB is 1, circulate to LSB                   |  |

| 7: $Set(T_{out}, n-1);$                                                                                                                        |                                                |  |

| 8: else                                                                                                                                        |                                                |  |

| 9: $Set(T_{out}, i-1);$                                                                                                                        |                                                |  |

| 10: end if                                                                                                                                     |                                                |  |

| 11: end if                                                                                                                                     |                                                |  |

| 12: Combine $(T_{in}; b_{on}, b_{off});$                                                                                                       |                                                |  |

| 13: end for                                                                                                                                    |                                                |  |

| 14: end procedure                                                                                                                              |                                                |  |

5) Circular Right Shift: In circular right shift, all the bits except the right most bit (LSB) is shifted to the right, and the LSB is circulated to MSB. Algorithm 14 performs the circular right shift of *n*-bit number kept in test tube  $T_{in}$  and outputs the result in test tube  $T_{out}$ .

## Algorithm 14 Circular Right Shifter

| 1: procedure CIRCULARRIGHTSHIFT( $in : T_{in}, n; out : T_{out}$ ) |                                                                       |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|

| 2: Pour blank memory strands of <i>n</i>                           | : Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_{out}$ ; |  |  |

|                                                                    | <i>n</i> bits                                                         |  |  |

| 3: for all bit i do                                                |                                                                       |  |  |

| 4: Separate $(T_{in}, i, b_{on}, b_{off})$ ;                       |                                                                       |  |  |

| 5: <b>if</b> $b_{on}$ is not empty <b>then</b>                     | $\triangleright i^{th}$ bit of the number is 1                        |  |  |

| 6: <b>if</b> $i = n - 1$ then                                      | ▷ LSB is 1, circulate to MSB                                          |  |  |

| 7: $Set(T_{out}, 0);$                                              |                                                                       |  |  |

| 8: else                                                            |                                                                       |  |  |

| 9: $Set(T_{out}, i+1);$                                            |                                                                       |  |  |

| 10: end if                                                         |                                                                       |  |  |

| 11: end if                                                         |                                                                       |  |  |

| 12: Combine $(T_{in}; b_{on}, b_{off});$                           |                                                                       |  |  |

| 13: end for                                                        |                                                                       |  |  |

| 14: end procedure                                                  |                                                                       |  |  |

## C. Adder / Subtracter

Addition and subtraction are two basic operations of an ALU and have been performed by several authors till date [19], [22], [23] running in O(n) time. The most interesting among them is the approach proposed in [22]. As has been specified in section III, addition/subtraction algorithm proposed here is being adapted from this work [22] and modified to include it into current context, such as, different numbers being implemented on different strands in two different tubes *etc.*.. In this algorithm, two *n*-bit numbers are being represented by two different DNA strands in test tubes  $T_1$  and  $T_2$  and result of addition will be available in test tube  $T_{out}$  in the same format. The overflow of addition will be detected by the presence of a particular DNA strand in a test tube. Let us represent the overflow detecting DNA strand as some single strand  $< DNA >_{Overflow}$ . If after addition, overflow test tube is empty, no overflow has happened, and if that particular DNA strand is present, it signals that, an overflow has happened.

In this algorithm, two globally available test tubes  $T_c$  and  $T_{nc}$  are used. If the numbers are present in  $T_c$ , it represents there is a carry, otherwise it represents absence of carry. Along with input numbers  $T_1$  and  $T_2$ , another test tube  $T_{init}$  is being taken as input, which acts as the starting test tube containing the numbers. In practice, the formal  $T_{init}$  will always be either the global  $T_c$  or the global  $T_{nc}$ . Choosing  $T_{init}$  as  $T_{nc}$  means there is no carry input; choosing  $T_{init}$  as  $T_c$  means there is a carry input.

Algorithm 15 Adder with carry in

| 1: <b>procedure</b> ADDER $(in : T_1, T_2, n, T_{init}; out : T_{out}, T_{overflow})$<br>2: Pour blank memory strands of <i>n</i> bits, 0000, in $T_{out}$ ; |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                              |  |  |

| 3: Combine( $T_{init}; T_1, T_2$ );                                                                                                                          |  |  |

| 4: <b>for all</b> bit <i>i</i> from LSB to MSB <b>do</b>                                                                                                     |  |  |

| 5: <b>if</b> $T_{nc}$ is not empty <b>then</b>                                                                                                               |  |  |

| 6: Separate $(T_{nc}, i, b_{on}, b_{off})$ ;                                                                                                                 |  |  |

| 7: <b>if</b> neither $b_{on}$ nor $b_{off}$ is empty <b>then</b>                                                                                             |  |  |

| $\triangleright i^{th}$ bits of two numbers are different                                                                                                    |  |  |

| 8: Set $(T_{out}, i)$ ;                                                                                                                                      |  |  |

| 9: Combine $(T_{nc}; b_{on}, b_{off});$                                                                                                                      |  |  |

| 10: else if $b_{off}$ is empty then                                                                                                                          |  |  |

| $i^{th}$ bits of two numbers are                                                                                                                             |  |  |

| 11: Combine $(T_c; b_{on}, b_{off});$                                                                                                                        |  |  |

| 12: else                                                                                                                                                     |  |  |

| $\triangleright i^{th}$ bits of two numbers are                                                                                                              |  |  |

| 13: Combine $(T_{nc}; b_{on}, b_{off});$                                                                                                                     |  |  |

| 14: end if                                                                                                                                                   |  |  |

| 15: else                                                                                                                                                     |  |  |

| 16: Separate $(T_c, i, b_{on}, b_{off});$                                                                                                                    |  |  |

| 17: <b>if</b> neither $b_{on}$ nor $b_{off}$ is empty <b>then</b>                                                                                            |  |  |

| $\triangleright i^{th}$ bits of two numbers are different                                                                                                    |  |  |

| 18: Combine $(T_c; b_{on}, b_{off});$                                                                                                                        |  |  |

| 19: else if $b_{off}$ is empty then                                                                                                                          |  |  |

| $\triangleright i^{th}$ bits of two numbers are                                                                                                              |  |  |

| 20: $\operatorname{Set}(T_{out}, i);$                                                                                                                        |  |  |

| 21: Combine $(T_c; b_{on}, b_{off});$                                                                                                                        |  |  |

| 22: else                                                                                                                                                     |  |  |

| $\triangleright i^{th}$ bits of two numbers are                                                                                                              |  |  |

| 23: Set $(T_{out}, i)$ ;                                                                                                                                     |  |  |

| 24: Combine $(T_{nc}; b_{on}, b_{off});$                                                                                                                     |  |  |

| 25: end if                                                                                                                                                   |  |  |

| 26: end if                                                                                                                                                   |  |  |

| 27: end for                                                                                                                                                  |  |  |

| 28: if $T_c$ is not empty then                                                                                                                               |  |  |

| ▷ There is a carry after end of addition. An overflow occurre                                                                                                |  |  |

| 29: Pour $< DNA >_{Overflow}$ in $T_{overflow}$ ;                                                                                                            |  |  |

| 30: end if                                                                                                                                                   |  |  |

| 31: end procedure                                                                                                                                            |  |  |

|                                                                                                                                                              |  |  |

Now, to perform addition, as the initial carry bit needs to be 0, the two inputs need to be placed in  $T_{nc}$ . The addition of two

n bit numbers residing in  $T_1$  and  $T_2$  can now be performed as follows.

#### Algorithm 16 Addition

| 1: procedure ADD( $in: T_1, T_2, n; out: T_{out}, T_{overflow}$ )                 |

|-----------------------------------------------------------------------------------|

| 2: $T_1^C \leftarrow Substring(T_1, 0, n-1);$                                     |

| 3: $T_2^C \leftarrow Substring(T_2, 0, n-1);$                                     |

| 4: $\{\tilde{T}_{out}, T_{overflow}\} \leftarrow Adder(T_1^C, T_2^C, n, T_{nc});$ |

| 5: end procedure                                                                  |

Similarly 2's Complement subtraction can be performed by first performing *NOT* of second number and placing them in  $T_c$ , as follows.

## Algorithm 17 Subtraction

```

1: procedure SUBTRACT(in : T_1, T_2, n; out : T_{out}, T_{overflow})

2: T_1^C \leftarrow Substring(T_1, 0, n - 1);

3: T_2^C \leftarrow NOT(T_2, n);

4: \{T_{out}, T_{overflow}\} \leftarrow Adder(T_1^C, T_2^C, n, T_c);

5: end procedure

```

As an example, let us consider the addition of two 4-bit numbers 1101 and 1001. Now the addition will be performed as follows.

- 1) Take 0000 in  $T_{out}$ .

- 2) Take backup of both test tubes  $T_1$  and  $T_2$  in  $T_1^C$  and  $T_2^C$  respectively.

- 3) Pour both numbers from  $T_1^C$  and  $T_2^C$  into  $T_{nc}$ .

- 4) Now for bit 3, as  $T_{nc}$  is not empty, perform following steps as follows.

- a) Separate  $T_{nc}$  in two test tubes based on bit 3 in  $b_{on}$  and  $b_{off}$  respectively, thus giving  $b_{on} = \{1101, 1001\}$  and  $b_{off}$  is empty.

- b) So according to line 11 of algorithm 15, pour  $b_{on}$  back in  $T_c$ .

- 5) For bit 2, as  $T_{nc}$  is empty,

- a) Separate  $T_c$  in two test tubes based on bit 2 in  $b_{on}$  and  $b_{off}$  respectively, thus giving  $b_{off} = \{1101, 1001\}$  and  $b_{on}$  is empty.

- b) According to lines 23 and 24 of the algorithm respectively, set bit 2 in  $T_{out}$  and pour  $b_{off}$  back in  $T_{nc}$ .

- 6) For bit 1, as  $T_{nc}$  is not empty,

- a) Separate  $T_{nc}$  in two test tubes based on bit 1 in  $b_{on}$ and  $b_{off}$  respectively, thus giving  $b_{on} = \{1101\}$ and  $b_{off} = \{1001\}$ .

- b) So according to lines 8 and 9 of the algorithm respectively, set bit 1 in  $T_{out}$  and pour  $b_{on}$  and  $b_{off}$  back in  $T_{nc}$ .

- 7) For MSB  $(b_0)$ , as  $T_{nc}$  is not empty,

- a) Separate  $T_{nc}$  in two test tubes based on bit 0 in  $b_{on}$  and  $b_{off}$  respectively, thus giving  $b_{on} = \{1101, 1001\}$  and  $b_{off}$  is empty.

- b) So according to line 11 of the algorithm, pour  $b_{on}$  back in  $T_c$ .

- 8) As  $T_c$  is not empty, it detects overflow and pour  $< DNA >_{Overflow}$  in  $T_{overflow}$ .

- So, the result of the addition is 0110 with an overflow.

As it can be observed, to add two n bit numbers, for each bit, emptiness of either  $T_c$  or  $T_{nc}$  is being checked and depending on that, particular constant time operations are being performed. As in the given example, to add 1101 and 1001, total number of bio-molecular operations being performed after taking backup of the two test tubes are 12 (1 as pouring both test tubes in  $T_{nc}$ , 2 for bit 3, 3 for bit 2 and 1, and 2 operation for MSB, and finally pouring  $< DNA >_{Overflow}$  in  $T_{overflow}$  to signal overflow). So, in worst condition, after combining both in  $T_C$ , 3 bio-molecular operations will be performed for each bit and overflow will be signalled, giving 3n+2 operations. So, the addition/subtraction algorithm executes in O(n), since substring and NOT also execute in O(n) time.

## D. Multiplication

Booth's algorithm is an well known algorithm to perform 2's complement multiplication on conventional circuits. This algorithm works as follows.

- 1) Take the two binary numbers *x* and *y* to be multiplied. If negative, take the number in 2's complement format.

- 2) Set two registers *u* and *v* initially to 0. These two registers will hold the multiplication result after completion.

- 3) Set a single-bit register x' initially to 0. This register will hold the LSB of x.

- 4) Continue the following operations for the number of bits present in *x*,

- a) Look at the LSB of x, and the value of x'. Let us represent it as  $x_{LSB}[x-1]$ .

- b) If  $x_{LSB}[x-1] = 10$ , subtract y from u. Discard the overflow.

- c) If  $x_{LSB}[x 1] = 01$ , add y to u. Discard the overflow.

- d) Perform Arithmetic Right Shift on *u* and *v*.

- e) Copy LSB of x in x'.

- f) Perform Circular Right Shift on x.

To perform multiplication operation, the output will be provided as two separate strands, corresponding to u and v, in two separate test tubes  $T_U$  and  $T_V$  respectively. The two *n*bit operands x and y are being taken as inputs in two separate test tubes  $T_X$  and  $T_Y$  respectively. Another test tube  $T_{X1}$  will contain single strand DNA  $\langle DNA \rangle_{X1}$ , if x' is 1, otherwise it will be empty. The algorithm will be as follows.

## Algorithm 18 Multiplier

| 1: procedure MULTIPLY( $in: T_X, T_Y, n; out: T_U, T_V$ ) |                                                                                 |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------------|--|

| · ·                                                       |                                                                                 |  |

| 2:                                                        | Discard( $T_{X1}$ ), if not already empty;                                      |  |

| 3:                                                        | Pour blank memory strands of n bits, $0000$ , in $T_U$ ;                        |  |

|                                                           |                                                                                 |  |

| 4.                                                        | <b>P</b> ower block in $T$ is a second set of $n$ bits of $n$ bits              |  |

| 4:                                                        | Pour blank memory strands of <i>n</i> bits, $0000$ , in $T_V$ ;                 |  |

|                                                           | <i>n</i> bits                                                                   |  |

| 5:                                                        | for number of bits in x do                                                      |  |

| 6:                                                        |                                                                                 |  |

|                                                           | Separate $(T_X, n-1, b_{on}, b_{off})$ ;<br>$\triangleright$ Identify $x_{LSB}$ |  |

| 7:                                                        | if $b_{on}$ is not empty and $T_{X1}$ is empty then                             |  |

|                                                           | $\triangleright x_{LSB}[x-1] = 10$ . Perform Subtraction $(u-y)$                |  |

| 8:                                                        | $\{T_{out}, T_{overflow}\} \leftarrow Subtract(T_U, T_Y, n);$                   |  |

| 9:                                                        | $Discard(T_{overflow});$                                                        |  |

| 10:                                                       | $Discard(T_U);$                                                                 |  |

| 11:                                                       | $Combine(T_U; T_{out});$                                                        |  |

```

12:

else

if b_{off} is not empty and T_{X1} is not empty then

13:

\triangleright x_{LSB}[x-1] = 01. Perform Addition (u+y)

\{T_{out}, T_{overflow}\} \leftarrow Add(T_U, T_Y, n);

14:

Discard(T_{overflow});

15:

Discard(T_{II});

16:

17:

Combine(T_U; T_{out});

18:

end if

19.

end if

Combine(T_X; b_{on}, b_{off});

\triangleright Arithmetic Right Shift of u and v

20:

21:

T_V^1 \leftarrow LogicalRightShift(T_V, n);

22:

Discard(T_V);

23:

Combine(T_V; T_V^1);

24:

Separate(T_U, n-1, b_{on}, b_{off});

25:

if b_{on} is not empty then

\triangleright Set MSB of v = LSB of u

26:

Set(T_V, 0);

27:

end if

28:

Combine(T_U; b_{on}, b_{off});

29:

T_{U}^{1} \leftarrow Arithmetic \tilde{Right}Shift(T_{U}, n);

Discard(T_U);

30:

31:

Combine(T_U; T_U^1);

Separate(T_X, n-1, b_{on}, b_{off});

32:

\triangleright Set (x-1) = x_{LSB}

33:

if b_{on} is not empty then

34:

Pour DNA strand \langle DNA \rangle_{X1} in T_{X1};

35:

else

Discard(T_{X1});

36:

37:

end if

38:

Combine(T_X; b_{on}, b_{off});

T_X^{temp} \leftarrow Circular RightShift(T_X, n); \triangleright Circular Right

39:

Shift of x

40:

Discard(T_X);

Combine(T_X; T_X^{temp});

41:

42:

end for

43: end procedure

```

#### E. Division

In an integer division operation, a 2n bit number is divided by an n bit number, and the result is obtained as two n bit numbers, one is quotient and the other one is remainder. Let us assume, the 2n bit dividend is being represented by two test tubes  $T_{DD}^1$  and  $T_{DD}^2$ , containing the upper half and lower half respectively, and the divisor is being represented by a single test tube  $T_{DR}$ . As an example, if the dividend is 9421, divisor is 117 and 8 bit calculation is considered, the dividend will be represented by 16 bit binary number (00100100 11001101), the upper half 00100100 will be stored in  $T_{DD}^1$ , the lower half 11001101 will be stored in  $T_{DD}^2$ , and the 8 bit binary representation of the divisor (01110101) will be stored in  $T_{DR}$ .

The general division algorithm works as follows.

- 1) Store upper half of dividend in R and lower half in Q.

- 2) For number of bits (which in this case is 8), repeat the following steps.

- 3) Left Shift RQ pair.

- 4) Subtract the divisor from R, and keep the result in R.

- 5) If R is positive, set right most bit in Q to 1.

- 6) Else Restore R by adding back the divisor.

At the end of the above procedure, Q will contain the quotient and R will contain the remainder.

Algorithm 19 Divider

| 1: procedure DIVISION( $in: T_{DD}^{1}, T_{DD}^{2}, T_{DR}, n; out: T_Q, T_R$ )<br>2: $T_R \leftarrow Substring(T_{DD}^{1}, 0, n - 1);$<br>3: $T_Q \leftarrow Substring(T_{DD}^{2}, 0, n - 1);$<br>4: for number of bits $n$ do $\triangleright$ Left Shift RQ pair<br>5: $T_{temp} \leftarrow LogicalLeftShift(T_R, n);$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4: <b>for</b> number of bits $n$ <b>do</b><br>5: $T_{temp} \leftarrow LogicalLeftShift(T_R, n);$ $\triangleright$ Left Shift RQ pair                                                                                                                                                                                      |

| 4: <b>for</b> number of bits $n$ <b>do</b><br>5: $T_{temp} \leftarrow LogicalLeftShift(T_R, n);$ $\triangleright$ Left Shift RQ pair                                                                                                                                                                                      |

| 4: <b>for</b> number of bits $n$ <b>do</b><br>5: $T_{temp} \leftarrow LogicalLeftShift(T_R, n);$ $\triangleright$ Left Shift RQ pair                                                                                                                                                                                      |

| 5: $T_{temp} \leftarrow LogicalLeftShift(T_R, n);$                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                           |

| 6: Discard $(T_R)$ ;                                                                                                                                                                                                                                                                                                      |

| 7: Combine $(T_R; T_{temp});$                                                                                                                                                                                                                                                                                             |

| 8: Separate $(T_Q, 0, b_{on}, b_{off})$ ;                                                                                                                                                                                                                                                                                 |

| 9: <b>if</b> $b_{on}$ is not empty <b>then</b>                                                                                                                                                                                                                                                                            |

| 10: Set $(T_R, n-1)$ ; $\triangleright$ Set $R_{LSB} = Q_{MSB}$                                                                                                                                                                                                                                                           |

| 11: end if                                                                                                                                                                                                                                                                                                                |

| 12: Combine $(T_Q; b_{on}, b_{off});$                                                                                                                                                                                                                                                                                     |

| 13: $T_{temp} \leftarrow LogicalLeftShift(T_Q, n);$                                                                                                                                                                                                                                                                       |

| 14: $\operatorname{Discard}(T_Q);$                                                                                                                                                                                                                                                                                        |

| 15: Combine $(T_Q; T_{temp});$                                                                                                                                                                                                                                                                                            |

| 16: $\{T_{out}, T_{overflow}\} \leftarrow Subtract(T_R, T_{DR}, n); \triangleright Subtract$                                                                                                                                                                                                                              |

| divisor from R                                                                                                                                                                                                                                                                                                            |

| 17: Discard $T_{overflow}$ ;                                                                                                                                                                                                                                                                                              |

| 18: Discard $(T_R)$ ;                                                                                                                                                                                                                                                                                                     |