# **Lecture 3: Power Dissipation**

# CSCE 6933/5933 Advanced Topics in VLSI Systems

Instructor: Saraju P. Mohanty, Ph. D.

**NOTE**: The figures, text etc included in slides are borrowed from various books, websites, authors pages, and other sources for academic purpose only. The instructor does not claim any originality.

# Outline of the Talk

- Power and Energy

- Dynamic Power

- Static Power

- Low Power Design

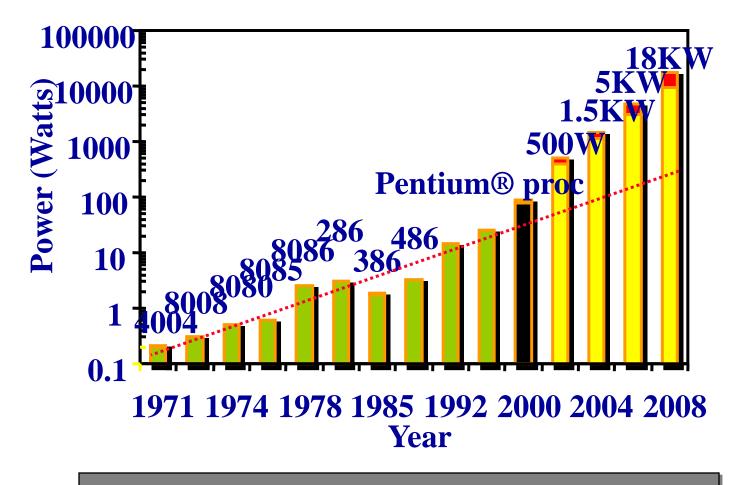

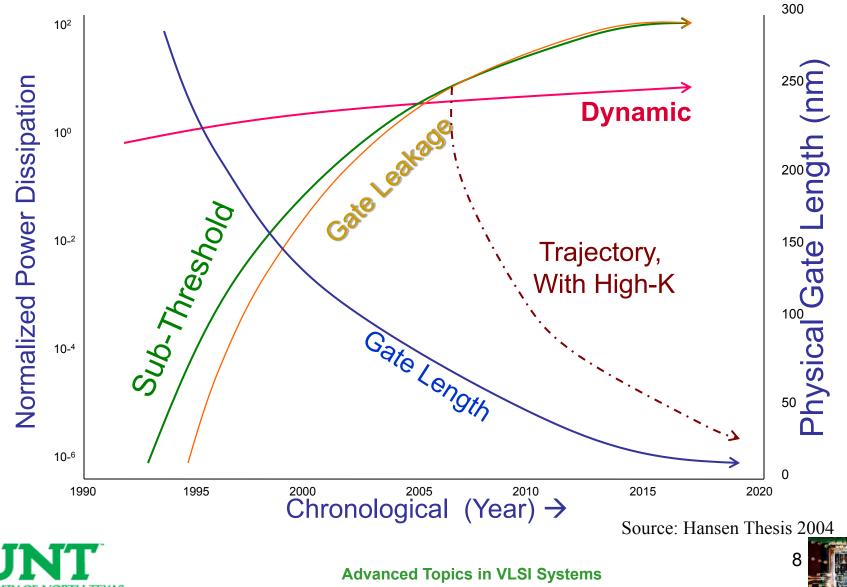

## **Power Dissipation Trend**

#### **Power Dissipation Trend**

Power delivery and dissipation will be prohibitive

#### Why Low-Power? .....

6

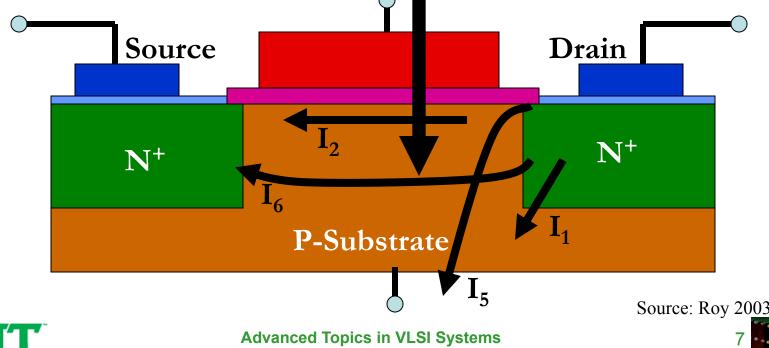

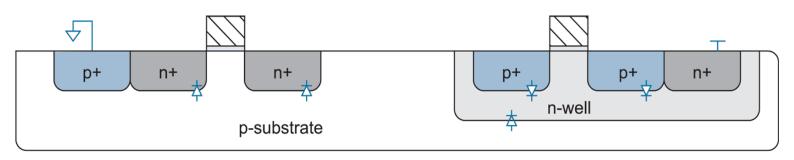

# Leakages in CMOS

- I<sub>1</sub> : reverse bias pn junction (both ON & OFF)

- I<sub>2</sub>: subthreshold leakage (OFF)

- $I_3$ : Gate Leakage current (both ON & OFF)

- $I_4$ : gate current due to hot carrier injection (both ON & OFF)

- $I_5$ : gate induced drain leakage (OFF)

- I<sub>6</sub> : channel punch through current (OFF)

# **Power Dissipation Redistribution**

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

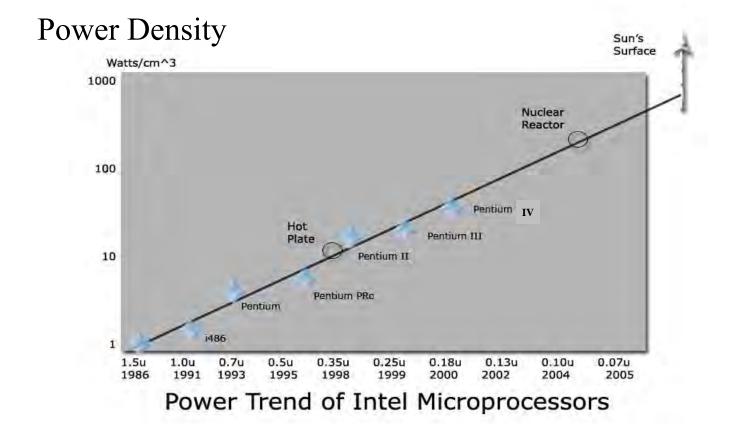

### **Dynamic and Static Power Sources**

#### Power Dissipation in CMOS : Dynamic

Capacitance Switching Current: This flows to charge and discharge capacitance loads during logic changes.

Short-Circuit Current: This is the current due to the DC path between the supply and ground during output transition.

#### Power Dissipation in CMOS : Static

- Subthrehold Current: Sub-threshold current that arises from the inversion charges that exists at the gate voltages below the threshold voltage.

- Tunneling Current: There is a finite probability for carrier being pass through the gate oxide. This results in tunneling current thorough the gate oxide.

- Reverse-biased Diode Leakage: Reverse bias current in the parasitic diodes.

- Contention Current in Ratioed Circuits: Ratioed circuits burn power in fight between ON transistors

#### Power Dissipation in CMOS : Dynamic

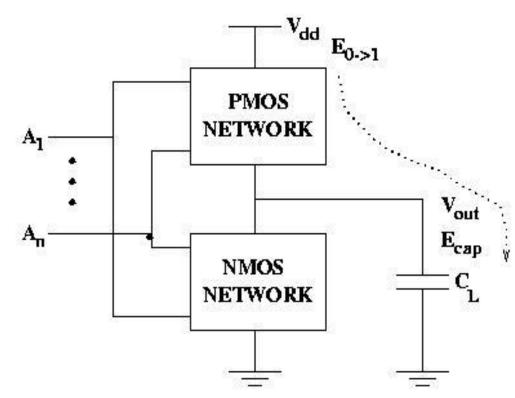

# A general CMOS transistor circuit

Discover the power of ideas

•Dynamic power is required to charge and discharge load capacitances when transistors switch.

- •One cycle involves a rising and falling output.

- •On rising output, charge Q = CLVDD is required.

- •On falling output, charge is dumped to GND.

#### Power Dissipation in CMOS : Dynamic

$$\mathbf{E}_{0\rightarrow 1} = \int_{0}^{T} \mathbf{P}(t) dt = \mathbf{V}_{dd} \int_{0}^{T} \mathbf{i}_{supply}(t) dt = \mathbf{V}_{dd} \int_{0}^{V_{dd}} \mathbf{C}_{L} d\mathbf{V}_{out} = \mathbf{C}_{L} \mathbf{V}_{dd}^{2}$$

$$E_{out} = \int_{0}^{T} P_{out}(t) dt = \int_{0}^{T} V_{out} i_{out}(t) dt = \int_{0}^{V_{dd}} C_{L} V_{out} dV_{out} = \frac{1}{2} C_{L} V_{dd}^{2}$$

#### Note:

- 1. the difference between the two is the loss

- 2. Energy doesn't depend on frequency

Power Dissipation in CMOS : Dynamic For  $N_c$  clock cycles energy loss :

$$\mathbf{E}_{\mathbf{N}_{\mathbf{C}}} = \mathbf{C}_{\mathbf{L}} \mathbf{V}_{\mathbf{d}\mathbf{d}}^2 \mathbf{n}(\mathbf{N}_{\mathbf{c}})$$

$n(N_c)$  : is the number of 0->1 transitions in N<sub>c</sub> clock cycles

$$P_{avg} = \lim_{N \to inf} \left[ \frac{E_{N_c}}{N_c} \right] f = \left[ \lim_{N \to inf} \frac{n(N_c)}{N_c} \right] C_L V_{dd}^2 f$$

$$= \alpha_{0 > 1} C_L V_{dd}^2 f$$

Note: Power depends on frequency

# Short Circuit Current

- When transistors switch, both NMOS and PMOS networks may be momentarily ON at once.

- Leads to a blip of "short circuit" current.

- < 10% of dynamic power if rise/fall times are comparable for input and output.

# Static Power : Subthrehold Current

- In OFF state, undesired leakage current flow.

- It contributes to power dissipation of idle circuits.

- If  $v_t$  is the thermal voltage and  $I_0$  is the current at  $V_{th}$  then the subthreshold current is :

$$I_{ds} = I_0 \left[ 1 - \exp\left(-\frac{V_{ds}}{v_t}\right) \right] \cdot \exp\left(\frac{V_{gs} - V_{th} - V_{off}'}{nv_t}\right) \qquad I_o = \mu C_{ox} \left(\frac{W}{L}\right) v_t^{2} e^{1.8}$$

- Drain-Induced-Barrier-Lowering (DIBL) an prominent effect for short channel transistors also impacts subthreshold conduction by lowering  $V_{th}$ .

- It increases as the  $V_{th}$  decreases or  $V_{gs}$  increases.

- It increases as the temperature increases.

#### Static Power : Junction Leakage

- The pn junctions between diffusion, substrate and well are all junction diodes.

- These are revered biased as substrate is connected to GND and well connected to  $V_{dd}$ .

- However, reversed biased diode also conduct small amount of current.

Reverse-biased diodes in CMOS circuits

#### Static Power : Junction Leakage

The reverse-biased junction current is expressed as follows: (D is not for drain, S is not for source)

$$I_{\rm D} = I_{\rm S} \left[ \exp \left( V_{\rm D} / v_{\rm T} \right) - 1 \right]$$

- I<sub>S</sub> depends on the doping level, the area, and perimeter of the diffusion region.

- $V_D$  is the diode voltage e.g.  $V_{sb}$  or  $V_{db}$ .

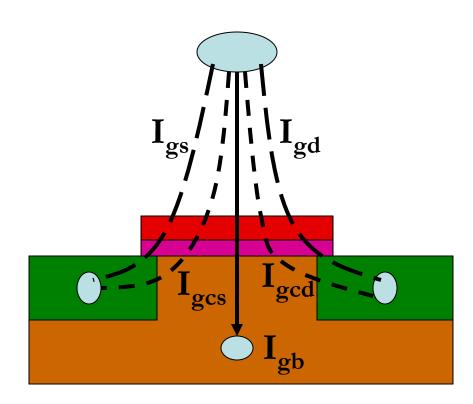

# **Static Power : Tunneling**

**BSIM4** Model

- •There is a finite probability for carrier being pass through the gate oxide.

- •This results in tunneling current thorough the gate oxide.

- •The effect is predominate for lower oxide thickness.

# **Static Power : Tunneling**

The gate oxide leakage current can be expressed as follows [Kim2003, Chandrakasan2001] (K and α are experimentally derived factors).

$I_{gate} = K W_{gate} (V_{dd} / T_{gate})^2 \exp(-\alpha T_{gate} / V_{dd})$

- Options for reduction of gate leakage power :

- Decreasing of supply voltage  $V_{dd}$  (will play its role)

- Increasing gate SiO<sub>2</sub> thickness T<sub>gate</sub> (opposed to the technology trend !!)

- Decreasing gate width W<sub>gate</sub> (only linearly dependent)

#### Low-Power Design

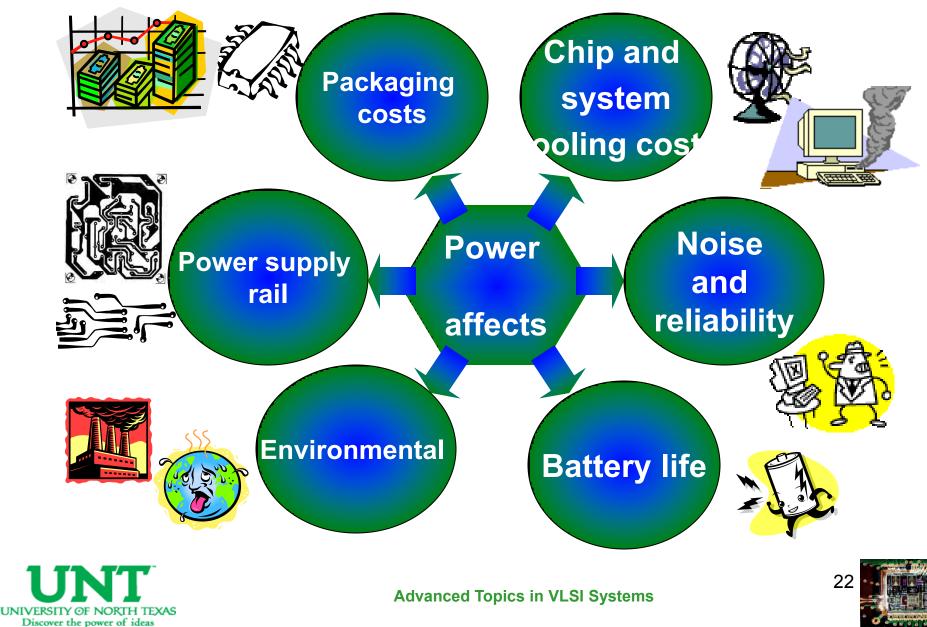

# Why Low Power?

# Various forms of Power Profile

- Average Power

- Total Energy

- Energy-Delay-Product (EDP)

- Power-Delay-Product (PDP)

- Power-Square-Delay-Product (PSDP)

- Peak Power

- Transient Power

- Cycle Difference Power

- Peak Power Differential

- Cycle-to-Cycle Power Gradient (Fluctuation)

- and many more .....

# Why peak power reduction ?

- To maintain supply voltage levels

- To increase reliability

- To use smaller heat sinks

- To make packaging cheaper

# Why Average Power/ Energy reduction ?

- To increase battery life time

- To enhance noise margin

- To reduce energy costs

- To reduce use of natural resources

- To increase system reliability

# Why Transience / Fluctuation Minimization ?

- To reduce power supply noise

- To reduce cross-talk and electromagnetic noise

- To increase battery efficiency

- To increase reliability

# Low-power design: Key Principles

>Using the lowest possible supply voltage.

- Using the smallest geometry, highest frequency devices, but operating them at lowest possible frequency.

- Using parallelism and pipelining to lower required frequency of operation.

- Power management by disconnecting the power source when the system is idle.

# Voltage, Frequency and Power Trade-offs

- Reduce Supply Voltage (V<sub>dd</sub>): delay increases; performance degradation

- Reduce Clock Frequency (f): only power saving no energy

- Reduce Switching Activity (N or E(sw)): no switching no power loss !!! Not in fully under designers control. Switching activity depends on the logic function. Temporal/and spatial correlations difficult to handle.

- Reduce Physical Capacitance: done by reducing device size reduces the current drive of the transistor making the circuit slow

#### How Much is Saved ?? Varying V<sub>dd</sub> / f

| Voltage (V <sub>dd</sub> ) | Frequency (f)           | Power (P <sub>d</sub> ) | Energy (E <sub>d</sub> ) |

|----------------------------|-------------------------|-------------------------|--------------------------|

| V <sub>dd</sub>            | <b>f</b> <sub>max</sub> | P <sub>d</sub>          | E <sub>d</sub>           |

| V <sub>dd</sub> / 2        | f <sub>max</sub> *      | P <sub>d</sub> / 4      | E <sub>d</sub> / 4       |

| V <sub>dd</sub> / 2        | f <sub>max</sub> / 2    | P <sub>d</sub> / 8      | E <sub>d</sub> / 4       |

| V <sub>dd</sub>            | f <sub>max</sub> / 2    | P <sub>d</sub> / 2      | E <sub>d</sub>           |

\* Note :

$$f_{max}$$

Vs f

### Low Power Design : Static Reduction

- Reduce static power:

- Selectively use ratioed circuits.

- Selectively use low V<sub>th</sub> devices.

- Leakage reduction:

Stacked devices, body bias, low temperature.