# Lecture 2: Nano-CMOS Issues

# CSCE 6933/5933 Advanced Topics in VLSI Systems

Instructor: Saraju P. Mohanty, Ph. D.

**NOTE**: The figures, text etc included in slides are borrowed from various books, websites, authors pages, and other sources for academic purpose only. The instructor does not claim any originality.

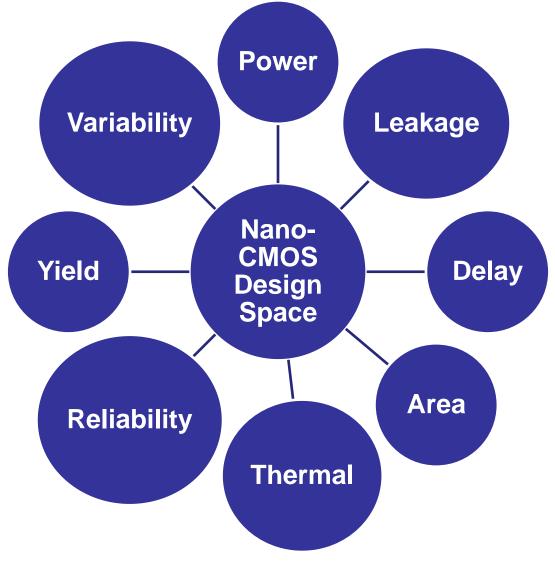

### Nano-CMOS Circuit: Design Space

Issues in Nano-CMOS Circuits ...

- Variability: Variability in process and design parameters has increased. They affect design decisions, yield, and circuit performance.

- Leakage: Leakage is increasing. Affects average as well as peak power metrics. Most significant for applications where system goes to standby mode very often, e.g. PDAs.

- **Power**: Overall chip power dissipation increasing. Affect energy consumption, cooling costs, packaging costs.

### **Issues in Nano-CMOS Circuits**

- Thermals or Temperature: Maximum temperature that can be reached by a chip during its operation is increasing. Affects reliability and cooling costs.

- **Reliability**: Circuit reliability is decreasing due to compound effects from variations, power, and thermals.

- Yield: Circuit yield is decreasing due to increased variability.

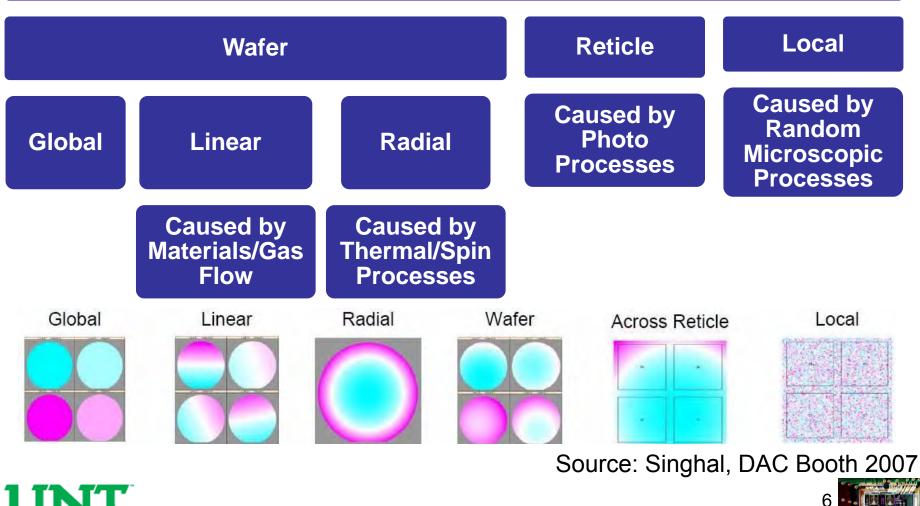

### Variability: Origin and Sources

- Ion implantation

- Chemical mechanical polishing (CMP)

- Chemical vapor deposition (CVD)

- Sub-wavelength lithography

- Lens aberration

- Materials flow

- Gas flow

- Thermal processes

- Spin processes

- Microscopic processes

- Photo processes

#### Source: Singhal, DAC Booth 2007

### Variability: Types ...

#### **Parametric Variations**

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

### Variability: Types ...

### Variability: Types ...

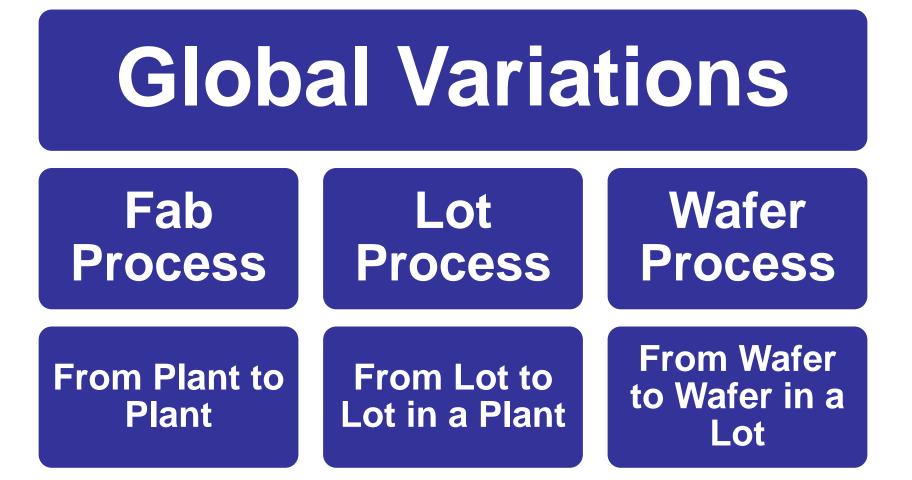

## **Variability Classifications**

#### Inter-Die or Intra-Die

#### Random or Systematic

#### Correlated or Uncorrelated

Spatial or Temporal

## Variability: Types

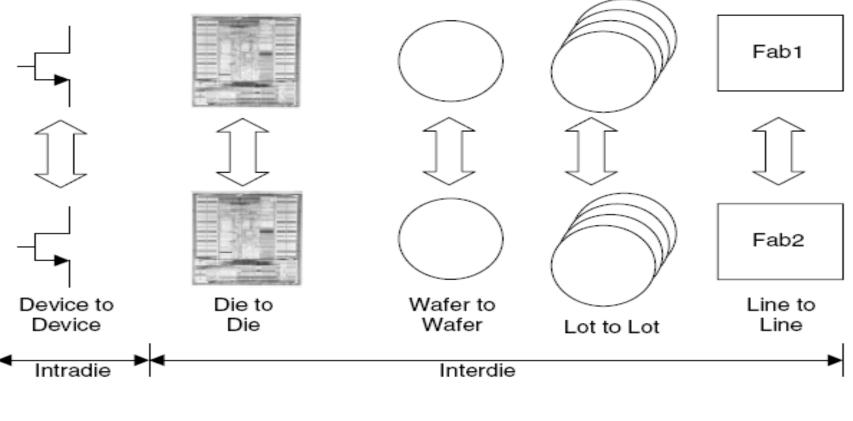

- Process variations are classified as:

- Inter-die and Intra-die.

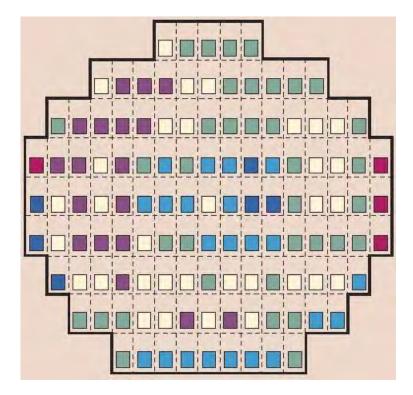

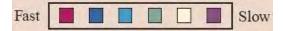

### Variability: The Impact in a Wafer ...

Source–drain resistance is different for different chips in a same die.

Gate-to-source and gate-to-drain overlap capacitance is different for different chips in a same die.

Source: Bernstein et al., IBM J. Res. & Dev., July/Sep 2006.

### Variability: The Impact in a Wafer

- The impact of process variations is seen as design yield loss.

- Digital circuits are typically optimized for speed and power.

- Analog circuits are designed to meet as many as five to ten performance metrics.

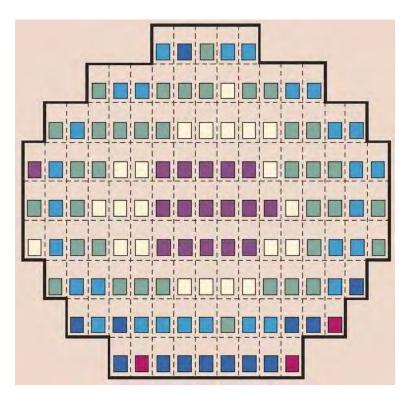

- Variations in process parameters have a resounding effect on the performance metrics of analog/mixed-signal and RF circuits.

- Figure showing impact of effective transistor channel length on the speed of an adder cell.

11

### Variability: The 15 Device Parameters

- 1) V<sub>DD</sub>: supply voltage

- 2) V<sub>Thn</sub>: NMOS threshold voltage

- 3) V<sub>Thp</sub>: PMOS threshold voltage

- 4) t<sub>gaten</sub>: NMOS gate dielectric thickness

- 5)  $t_{qatep}$ : PMOS gate dielectric thickness

- 6) L<sub>effn</sub>: NMOS channel length

- 7) L<sub>effp</sub>: PMOS channel length

- 8) W<sub>effn</sub>: NMOS channel width

- 9) W<sub>effp</sub>: PMOS channel width

- 10) N<sub>gaten</sub>: NMOS gate doping concentration

- 11) N<sub>gatep</sub>: PMOS gate doping concentration

- 12) N<sub>chn</sub>: NMOS channel doping concentration

- 13) N<sub>chp</sub>: PMOS channel doping concentration

- 14) N<sub>sdn</sub>: NMOS source/ drain doping concentration

- 15) N<sub>sdp</sub>: PMOS source/ drain doping concentration.

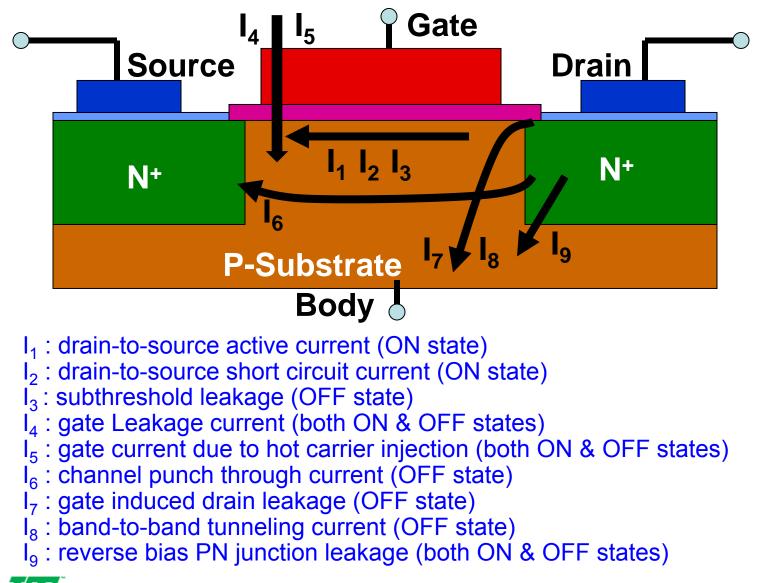

### Power and Leakage ...

Discover the power of ideas

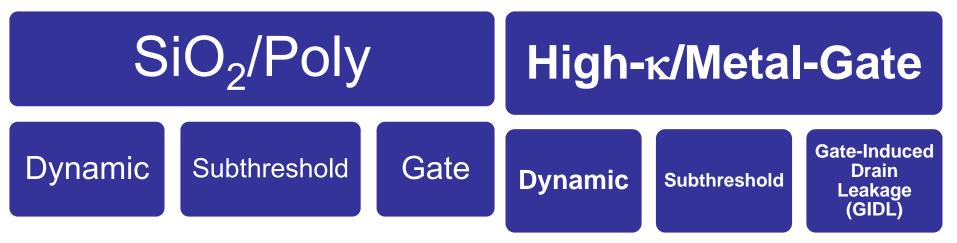

### Power and Leakage

- The relative prominence of these components depend on:

- Technology Node: 65nm, 45nm, or 32nm

- Process : SiO<sub>2</sub>/Poly or High-κ/Metal-Gate

• BTBT tunneling is important for sub-45nm.

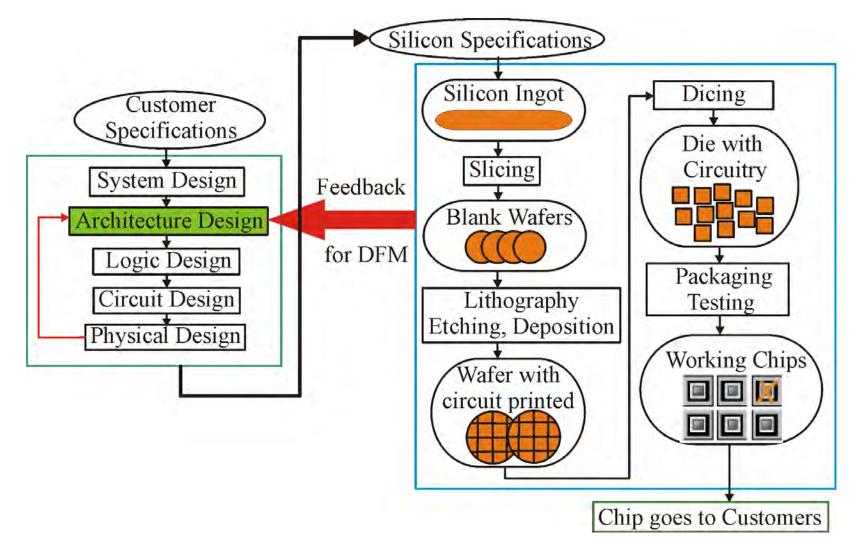

### Nano-CMOS Design: Feedback Needed

**Advanced Topics in VLSI Systems**

15