## Simscape<sup>®</sup> based Ultra-Fast Design Exploration of Graphene Nanoelectronic Systems

S. Joshi<sup>1</sup>, E. Kougianos<sup>2</sup> and S. P. Mohanty<sup>3</sup> NanoSystem Design Laboratory (NSDL, http://nsdl.cse.unt.edu) University of North Texas, Denton, TX 76203, USA.<sup>1,2,3</sup> Email: shitaljoshi@my.unt.edu<sup>1</sup>, eliask@unt.edu<sup>2</sup> and saraju.mohanty@unt.edu<sup>3</sup>

> Presented By Shital Joshi

### Table of contents

Introduction and motivation

□Novel contributions of this paper

□Simscape<sup>®</sup> Modeling of a Graphene FET

Graphene FET: Structure

GFET based Low-Noise Amplifier (LNA) circuit design

➢Simscape<sup>®</sup> modeling of the LNA

Conclusion and Directions for future research

References

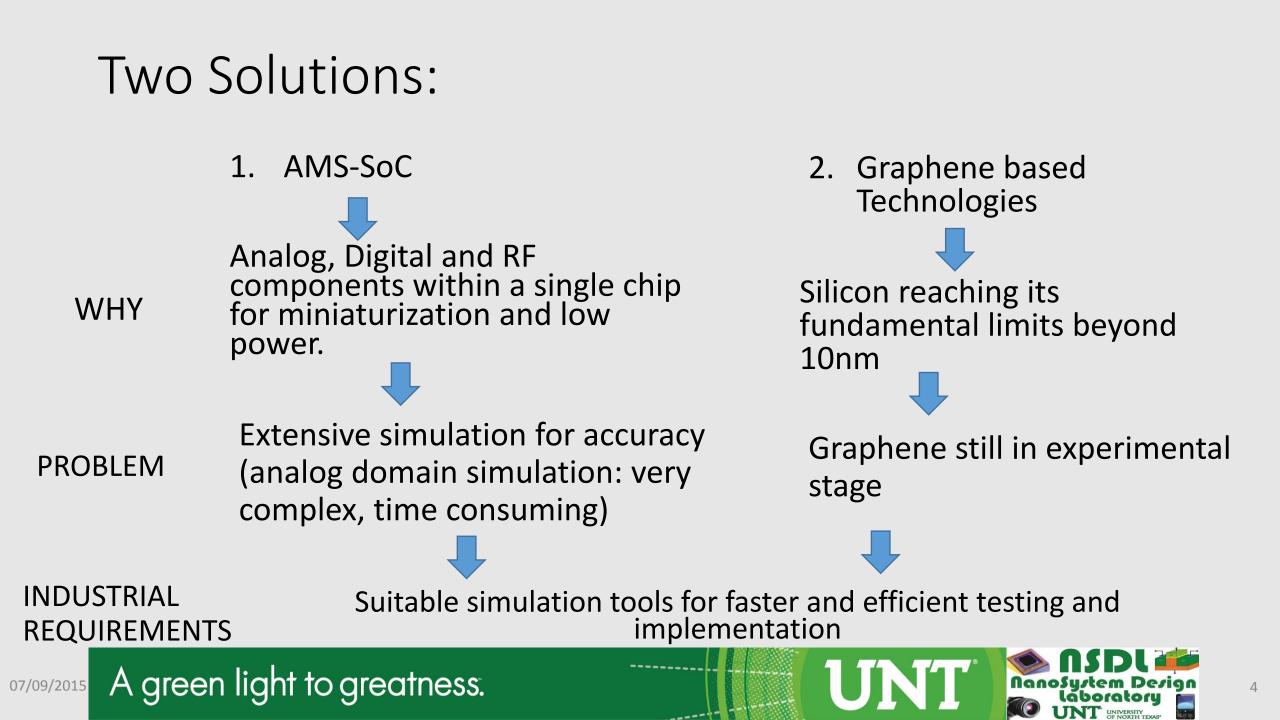

### Introduction and Motivation

Demand driven industry

Consumer Designer actions

Smaller, cheaper and low power consuming devices

Solutions:

Analog Mixed Signal-System on Chip (AMS-SoC)

➢Graphene based technologies

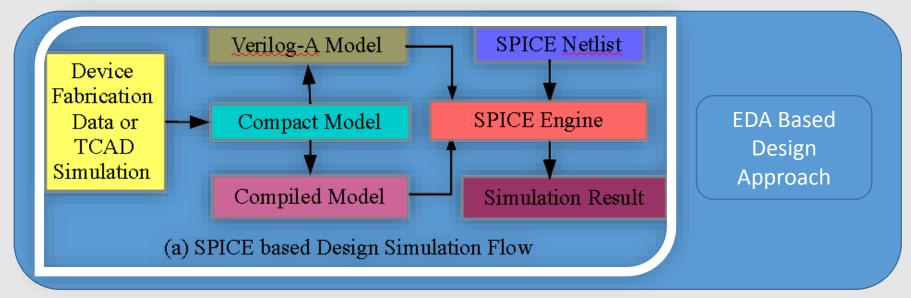

### Standard SPICE based Flow

Drawbacks associated with SPICE simulation:

- ➢ Heavy computational needs → Prolong design time + Increase nonrecurrent design cost

- ➢ Need of fab data or TCAD simulations → Not always available for new or emerging technologies,

- Limited design optimization support

### Proposed Simscape<sup>®</sup> based Flow

□ Simscape<sup>®</sup> based design flow offers distinct advantages over conventional SPICE:

➤ No need of fab data → Good platform to model emerging technologies

Fast and easy optimization at system level.

### Novel Contributions

- 1. A non- EDA (Simscape<sup>®</sup>) based ultra-fast design flow is explored.

- 2. Modeling of GFETs using Simscape<sup>®</sup>.

- 3. Modeling of a GFET based LNA using the Simscape<sup>®</sup> graphical environment.

- Experimental validation of the Simscape<sup>®</sup> device level models with results obtained in MATLAB<sup>®</sup>[I. Meric,2008], SPICE[R. Doe ,2013], VHDL-AMS[I. J. Umoh,2011] or Verilog-A[M. A. Khan,2014] models.

- 5. Characterization of GFET based case study circuit (LNA) and comparison with Verilog-A based designs.

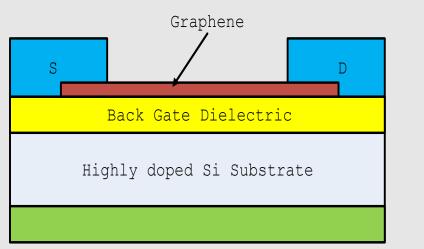

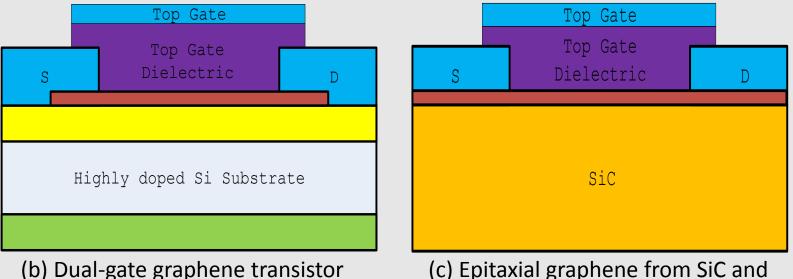

## Graphene FET

(a) Back-gated graphene transistor

transistor structure

□Semi-metallic nature → ρ<sub>ON</sub>/ρ<sub>OFF</sub> ~ 6 → I<sub>ON</sub>/I<sub>OFF</sub> < 10 at room temperature</li>

□Attractive for high-speed analog electronics, where transistor current gain is more important than I<sub>ON</sub>/I<sub>OFF</sub>

□Transistors having cut-off frequencies as high as 350 GHz

### How graphene can address future devices?

(a) Lightweight

(c) Strong

(b) Flexible

(d) Faster and High packing density

(e) Transparent

### All this with little change in current processing techniques !

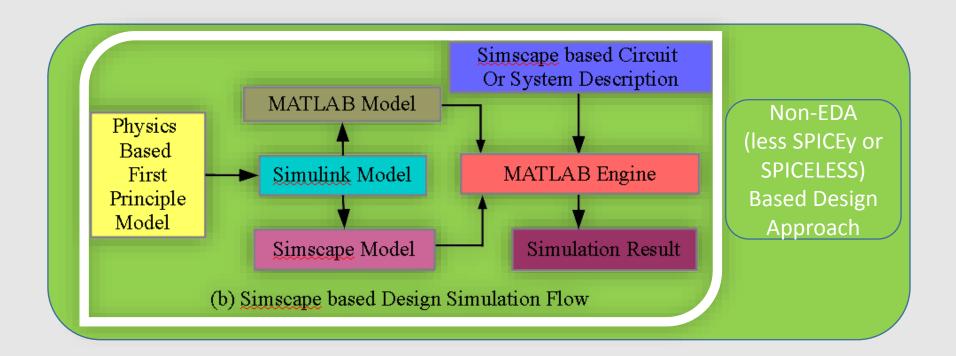

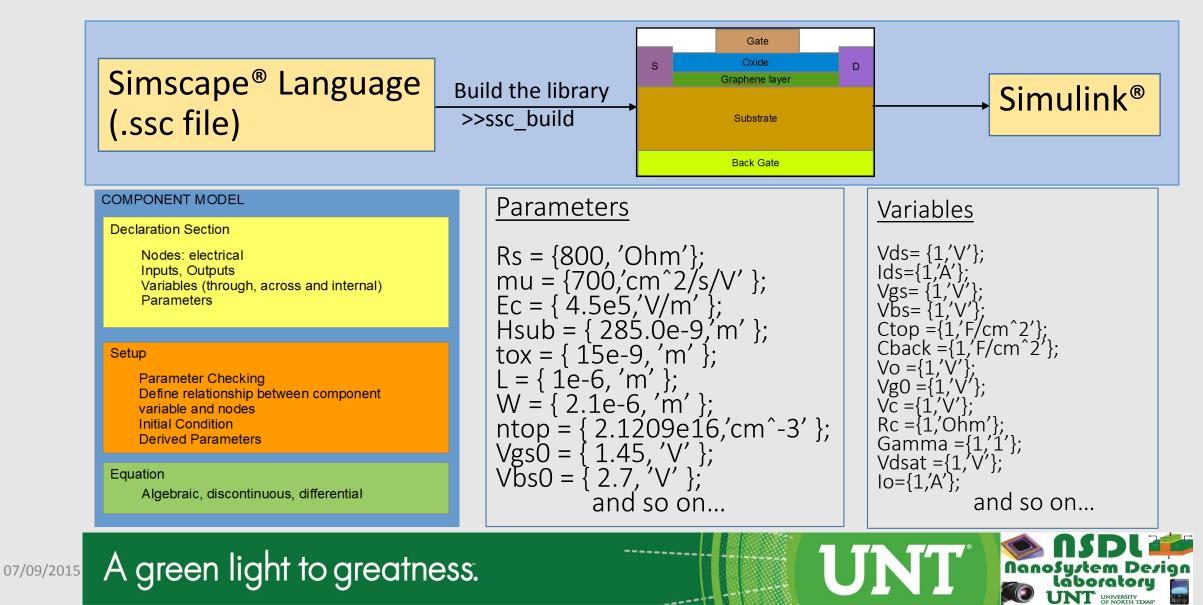

## Simscape<sup>®</sup> Modeling of GFET

Two ways to build custom Simscape<sup>®</sup> models:

- (i) Graphical method using fundamental Simulink<sup>®</sup>/Simscape<sup>®</sup> blocks

- Hard to build: may not be precise, interfacing problem linking different domains together.

- Less robust: May not work for all models and for all application.

- ➢Not reusable: May not be used for different applications.

UNT

### Continued...

- (i) Textually with the Simscape<sup>®</sup> physical modeling language

➢ Simscape<sup>®</sup> physical modeling language based on physical network approach.

- Offers better portability and is easier to maintain

Does not depend on the location of the input in the system.

Can handle algebraic constraints easily.

Easier modeling in multiple domains.

Makes hierarchical modeling and simulation of complex system easier as well.

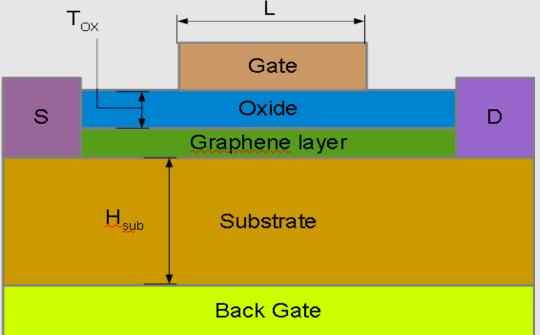

### Graphene FET: Structure

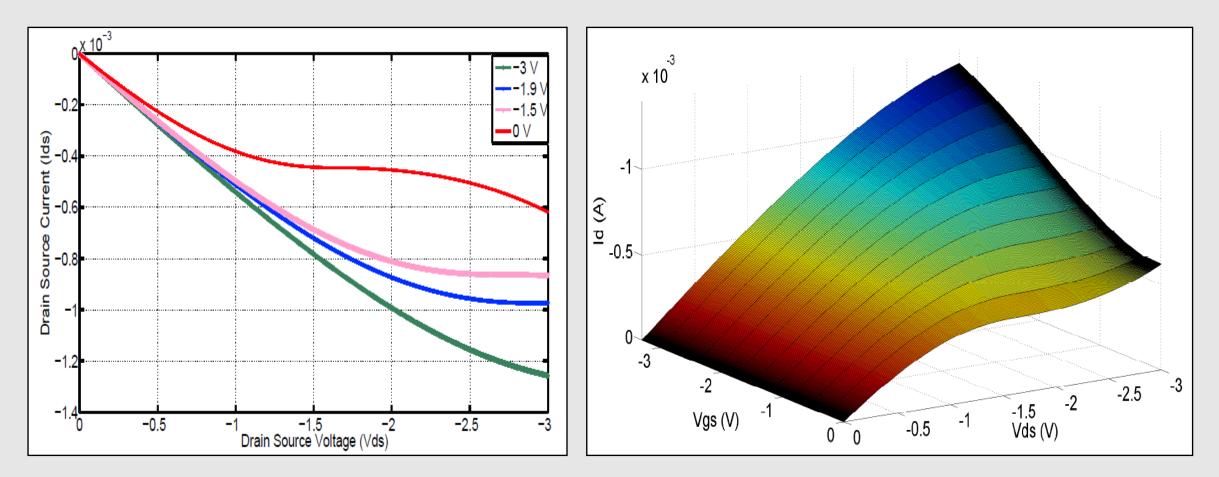

For a negative  $V_{bs}$ , the source/drain region is P-type mobility =  $700 \text{ cm}^2/\text{V} \text{ s}$ ,  $R_{s} = 800$ , and Case 1  $E_{c} = 4.5 \text{ kV/cm}.$

Top-gate voltages of 0 V, -1.5 V, -1.9 V and -3 V were used and  $V_{ds}$  is varied from 0 to -3 V.

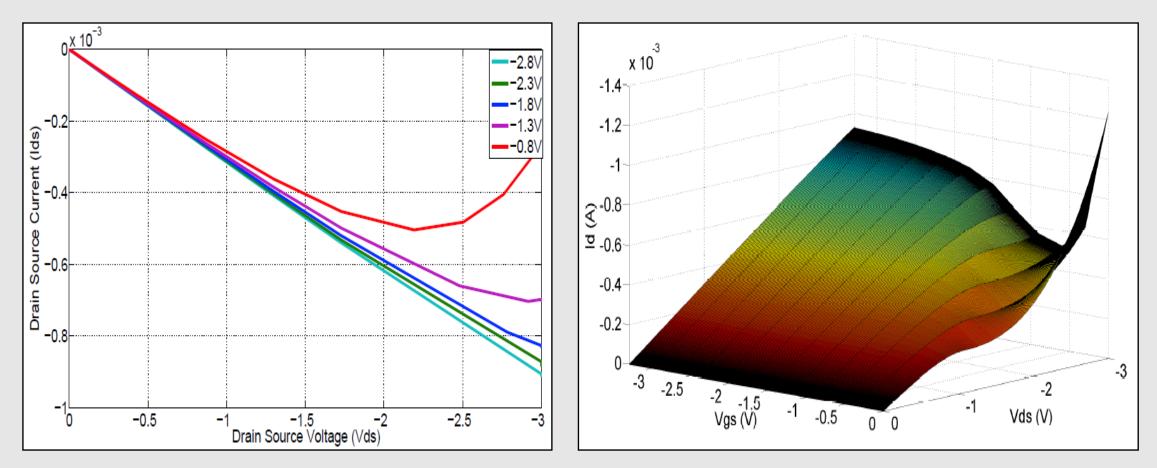

For positive V<sub>bs</sub>, the source/drain region is n-type mobility =  $1200 \text{ cm}^2/\text{V} \text{ s}$ ,  $R_{s} = 1500$  , and Case 2  $E_c = 15 \text{ kV/cm}.$

Top-gate voltages of -0.8 V, -1.3 V, -1.8 V, -2.3 V, and -2.8 V were used and  $V_{ds}$  is varied from 0 to -3 V.

### Gate Oxide S D Graphene layer Substrate Back Gate

### Fig. 1. Dual-gate GFET cross-section

The device parameters were selected are based on published results [5]

A green light to greatness. 07/09/2015

### Simscape<sup>®</sup> based Graphene Device Simulation

### Case 1: For negative V<sub>bs</sub>

Fig. 2. I-V Characteristics of continuous and discrete values of V<sub>gs</sub> for P-type GFET

<sup>07/09/2015</sup> A green light to greatness.

Nano

Case 2: For positive V<sub>bs</sub>

Fig. 3. I-V Characteristics of continuous and discrete values of V<sub>gs</sub> for N-type GFET

## Comparison with Results from VHDL-AMS[Umoh, 2011]

The result obtained from Simscape<sup>®</sup> is identical:

- For a top-gate voltage of 0 V, -1.5 V, -1.9 V and -3 V and a back gate voltage (Vbs) = -4.0 V, the drain current decreased with increase in the Vds and decrease in the top gate voltage.

- For a top-gate voltage of -0.8 V, -1.3 V, -1.8 V, -2.3 V and -2.8 V and a back gate voltage (Vbs) = +4.0 V, the drain current decreased with decrease in the top gate voltage.

I. J. Umoh and T. J. Kazmierski, "VHDL-AMS Model of A Dual Gate Graphene FET," in Proceedings of the Forum on Specification and Design Languages, 2011, pp. 1–5.

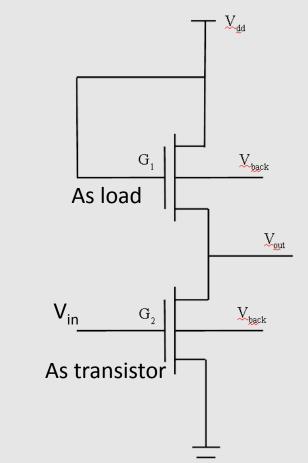

### GFET based LNA Circuit Design

□ High gain: better processing of signal for subsequent circuit stages and low noise

**Low NF**: better reception of signal

Non-linearity: Avoids blocking and intermodulation problems

Impedance matching: Maximizes power transfer and minimizes reflection

Note:

Both gain and NF vary with the operating frequency

➤Trade-off between gain and NF

Fig. 4. Schematic of a GFET based LNA circuit

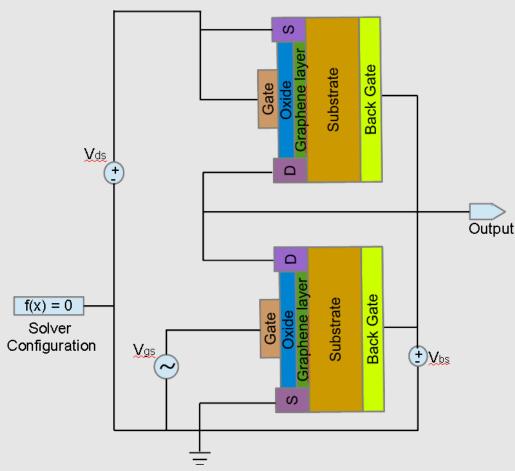

## Simscape<sup>®</sup> modeling of the LNA

#### Key Points:

Solver configuration is needed

Simulink-PS and PS-Simulink converter needed (for Simulink<sup>®</sup> Simuscape<sup>®</sup> block connection)

UNT

#### Fig. 5. Simscape® Experimental Setup for LNA modeling

## Simscape<sup>®</sup> modeling of the LNA

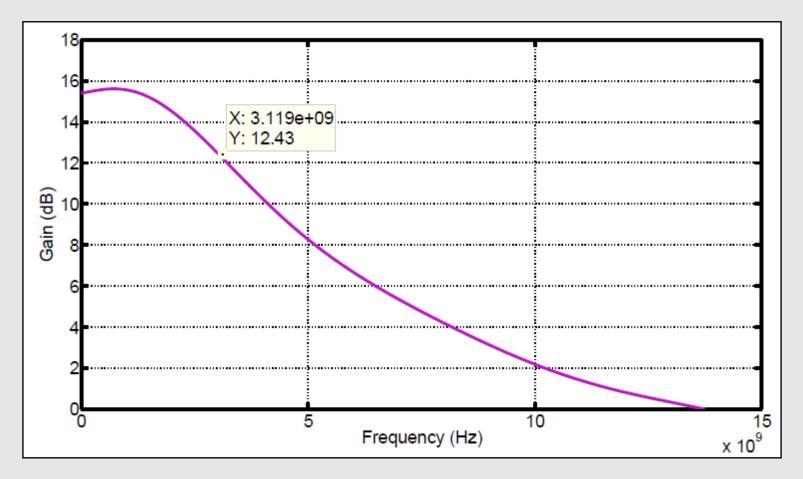

| Parameters                   | Values   | Values   |

|------------------------------|----------|----------|

| $W_1$                        | 20 nm    | 30 nm    |

| $W_2$                        | 10 nm    | 15 nm    |

| Gain (G)                     | 14.54 dB | 15.41 dB |

| Bandwidth ( $f_T$ )          | 3.12 GHz | 3.12 GHz |

| Power (P <sub>LNA</sub> )    | 23.8 mW  | 27.2 mW  |

| Table 1. GFET based LNA FoMs |          |          |

$\frac{\text{Note}}{\text{H}_{\text{sub}}} = 1 \text{ nm}$  $\text{H}_{\text{sub}} = 2.85 \text{ nm}$ L = 50 nm

Nanos

UNT

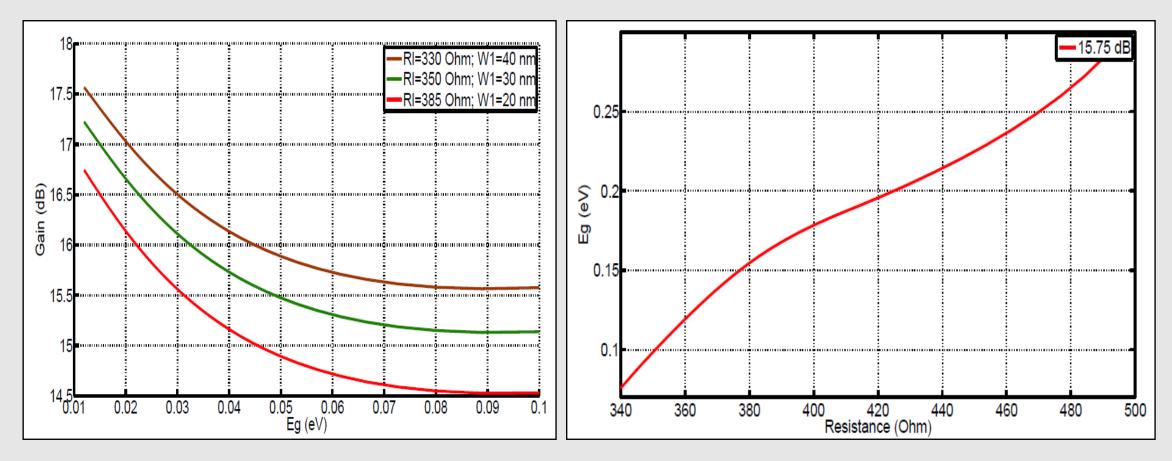

### Simulation Results

Fig. 6. Gain (G) vs  $E_g$  for different loads ( $R_L$ )

Fig. 7.  $E_g vs R_L$  at constant G = 15.75 dB

UNT UNVESTIGATION

### Continued...

Fig. 8. Simulated frequency characteristic of GFET based LNA

### Comparison with Results from [Das, 2011]

□ The result in Fig. 6 shows the inverse relationship between the band-gap and gain as given in [Das, 2011].

□ Similar result is obtained in Fig. 7 for bandwidth vs load resistance at a constant gain G = 15.75 dB.

S. Das and J. Appenzeller, "An All-graphene Radio Frequency Low Noise Amplifier," in Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2011, pp. 1–4

### Conclusions and Directions for Future Research

- Results show that Simscape<sup>®</sup> based models can be a substitute for EDA based models for exploratory design.

- As a future research, additional functionality for noise, transfer function and non-linear RF analyses such as periodic and quasi-periodic steady state can be incorporated within the Simscape<sup>®</sup> model.

- Particle swarm-based optimization (PSO) algorithms such as artificial bee colony and ant colony optimization for GFET based circuits will be explored within MATLAB<sup>®</sup> /Simscape<sup>®</sup>.

### References

- I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L. Shepard, "Current saturation in zero-bandgap, top-gated graphene field effect transistors," Nature Nanotechnology, vol. 3, pp. 654–659, November 2008.

- 2. R. Doe, "Graphene Field Effect Transistor Modelling," http://www.cnt.ecs.soton.ac.uk/gfet web/gfet web.html, Jan 2013.

- 3. I. J. Umoh and T. J. Kazmierski, "VHDL-AMS Model of A Dual Gate Graphene FET," in Proceedings of the Forum on Specification and Design Languages, 2011, pp. 1–5.

- 4. M. A. Khan, S. P. Mohanty, and E. Kougianos, "Statistical Process Variation Analysis of a Graphene FÉT based LC-VCO for WLAN Applications," in Proceedings of the 15th IEEE International Symposium on Quality Electronic Design (ISQED), 2014, pp. 569–574.

### Continued...

- F. Xia, D. B. Farmer, Y.-m. Lin, and P. Avouris, "Graphene Field-Effect Transistors with High On/Off Current Ratio and Large Transport Band Gap at Room Temperature," Nano Letters, vol. 10, no. 2, pp. 715–718, 2010.

- 6. S. Das and J. Appenzeller, "An All-graphene Radio Frequency Low Noise Amplifier," in Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2011, pp. 1–4.

# Thank you !!!