#### Ultra-Fast Variability-Aware Optimization of Mixed-Signal Designs using Bootstrapped Kriging

S. P. Mohanty<sup>1</sup>, E. Kougianos<sup>2</sup>, and V. P. Yanambaka<sup>3</sup> NanoSystem Design Laboratory (NSDL, http://nsdl.cse.unt.edu) University of North Texas, Denton, TX 76203, USA.<sup>1,2,3</sup> Email: saraju.mohanty@unt.edu<sup>1</sup>, elias.kougianos@unt.edu<sup>2</sup> and VenkataPrasanthYanambaka@my.unt.edu<sup>3</sup>

#### **Outline of the talk**

- Background and Motivation

- Novel Contributions

- Process Variation Aware Ultra-Fast Design

Optimization Flow for Mixed Signal Circuits

UN 12

- PSO Algorithm

- Conclusions

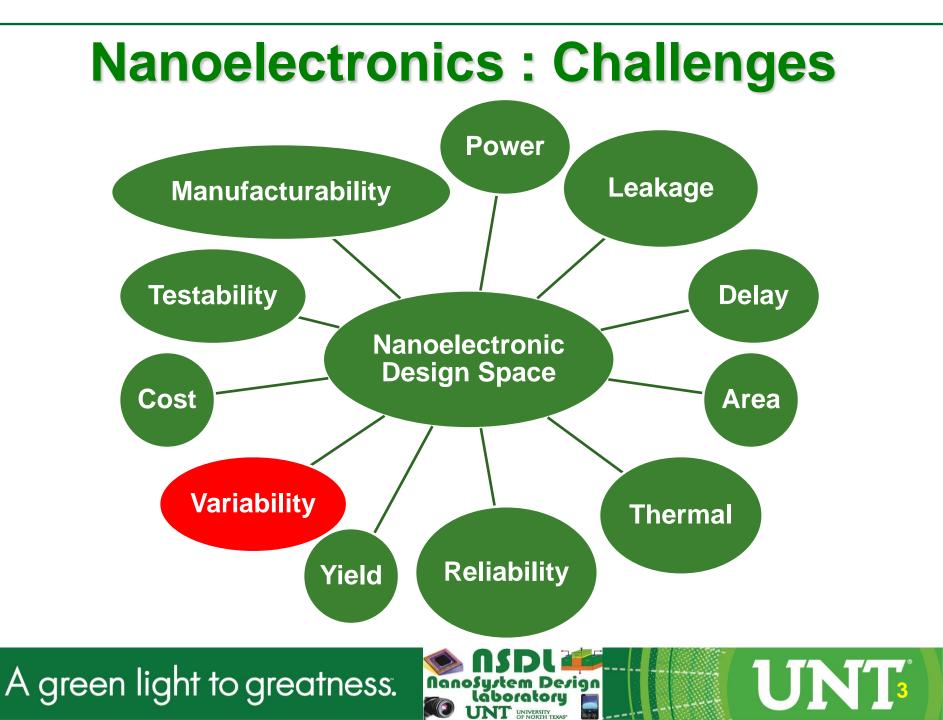

# **Nanoscale Variability : Overall**

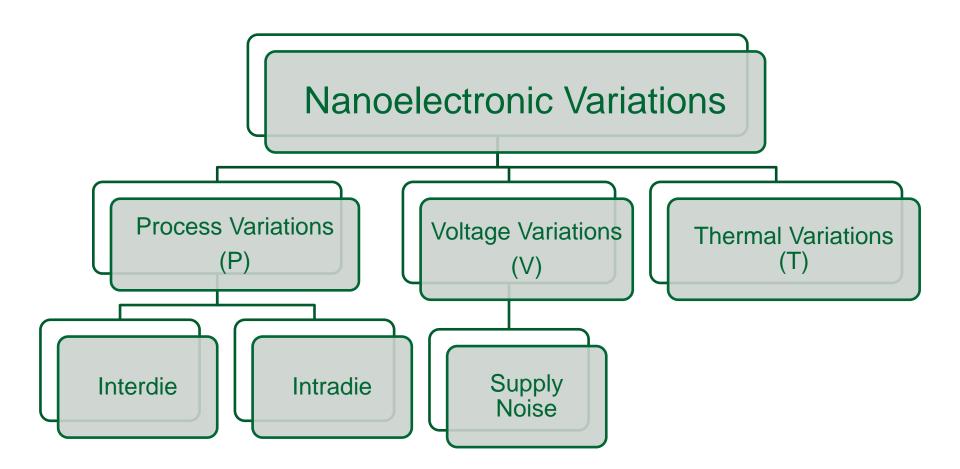

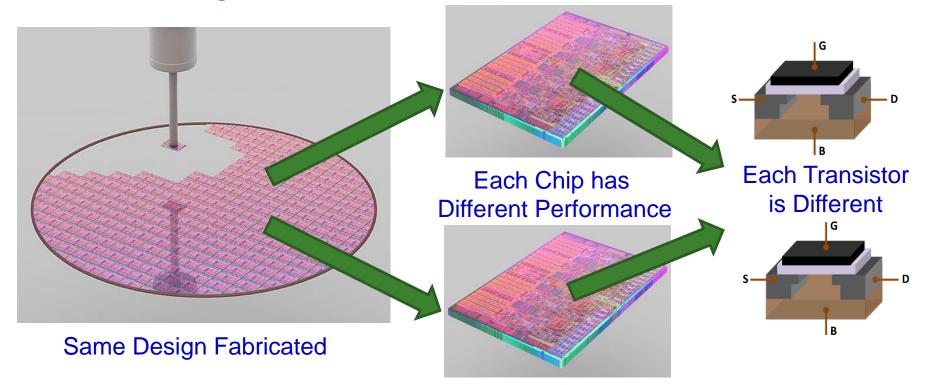

#### **Nanoelectronics Variability ?**

Discrepancy between chip parameters - Design Time versus Actual Post Fabrication

Source: http://apcmag.com/picture-gallery-how-a-chip-is-made.htm

#### **Research Questions**

- How process variations effects can be captured in the design cycle?

- How process variation effects can be mitigated in the design cycle?

- How to achieve the above two with minimal design cycle consumed?

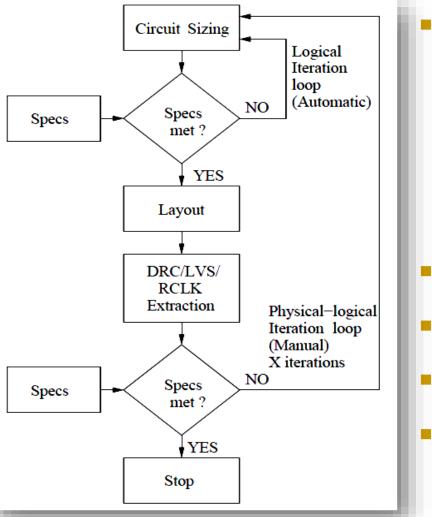

#### **Standard Design Flow – Very Slow**

A green light to greatness.

- Standard design flow requires multiple manual iterations on the back-end layout to achieve parasitic closure between front-end circuit and back-end layout.

- Longer design cycle time.

- Error prone design.

UNIVERSITY

- Higher non-recurrent cost.

- Difficult to handle nanoscale challenges.

UNT

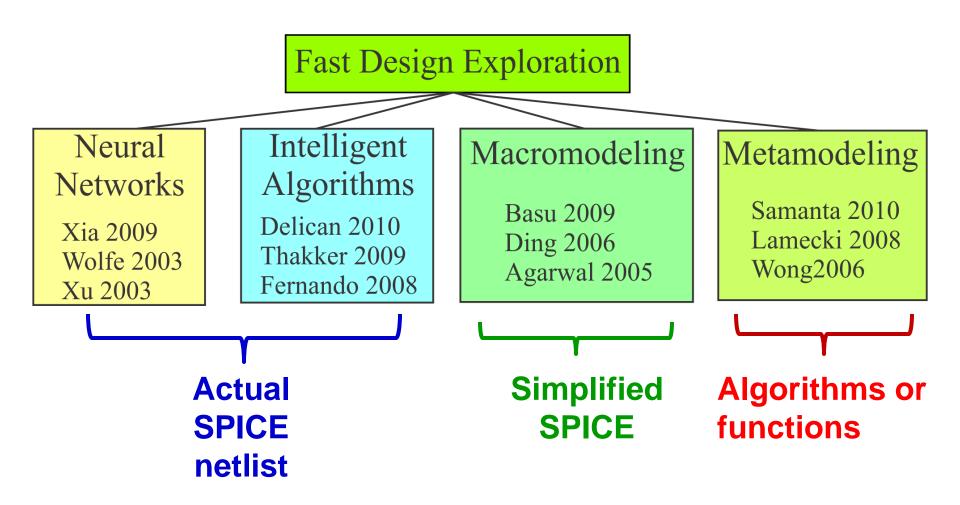

#### **Related Research: Fast Exploration**

**IJNT**®

#### **Related Research: Metamodels**

- One of the most common and reliable method used is Polynomial Regression

- Non-Polynomial metamodels built from Neural Networks have been reported to surpass Polynomial metamodels

- Weight training process is critical in developing Neural Network models

- Kriging training for Neural Networks provides tradeoff

between the accuracy of Kriging and scalability of NN

models

**UNT**<sup>9</sup>

# **Novel Contributions of This Paper**

- Fast and accurate physical design and optimization

- Adaption of PSO algorithm for nano-CMOS based process variation aware optimization

- Case study exploration using a 180nm CMOS based

PLL design

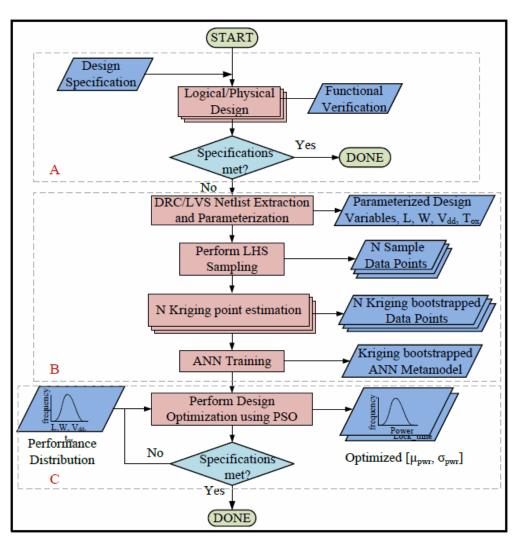

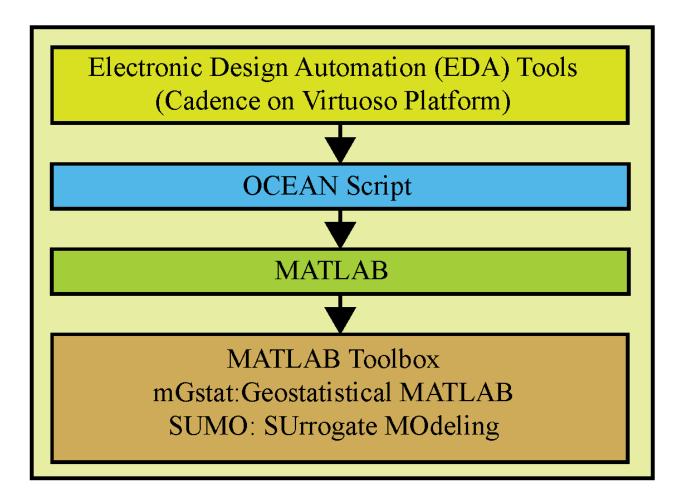

#### **Process Variation Aware Ultra-Fast Design Optimization Flow for Mixed-Signal Circuits**

# **Proposed Design Optimization Flow**

Derign

láboratory

UNIT UNIVERSITY

UNT<sup>1</sup>2

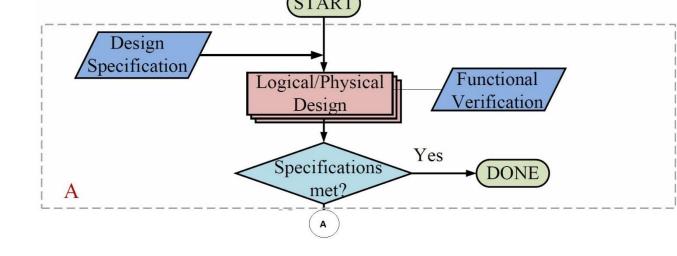

# Proposed Design Optimization Flow Part - A

- First phase consists of baseline logical and physical design

- Baseline is simulated for functional verification

- This verification also serves to characterize circuit design START objectives

UΝ

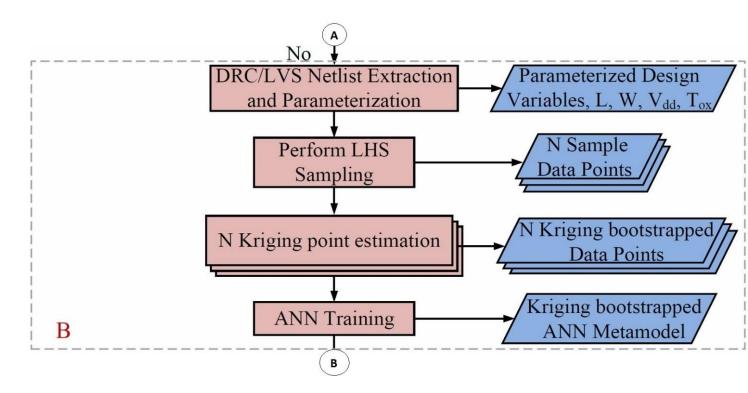

#### Proposed Design Optimization Flow Part - B

This phase involves creation of process variation aware

metamodel of the circuit design

UN

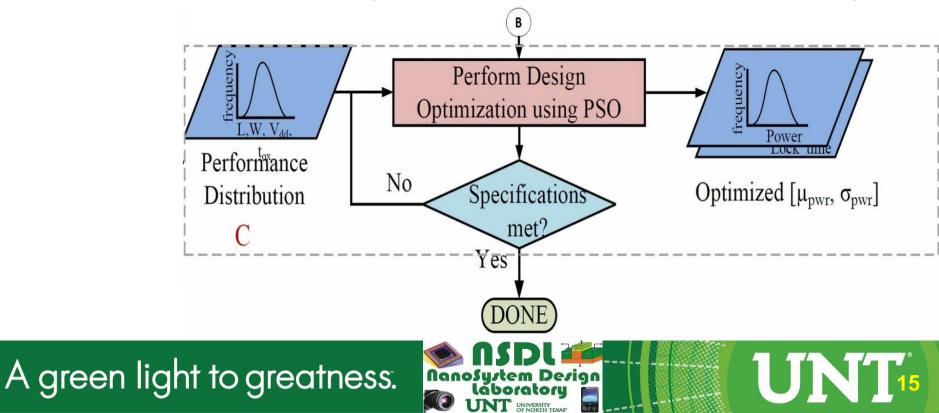

# Proposed Design Optimization Flow Part - C

- This phase is process aware design optimization

- The optimization algorithm is used with the created metamodel and design objectives to optimize the design

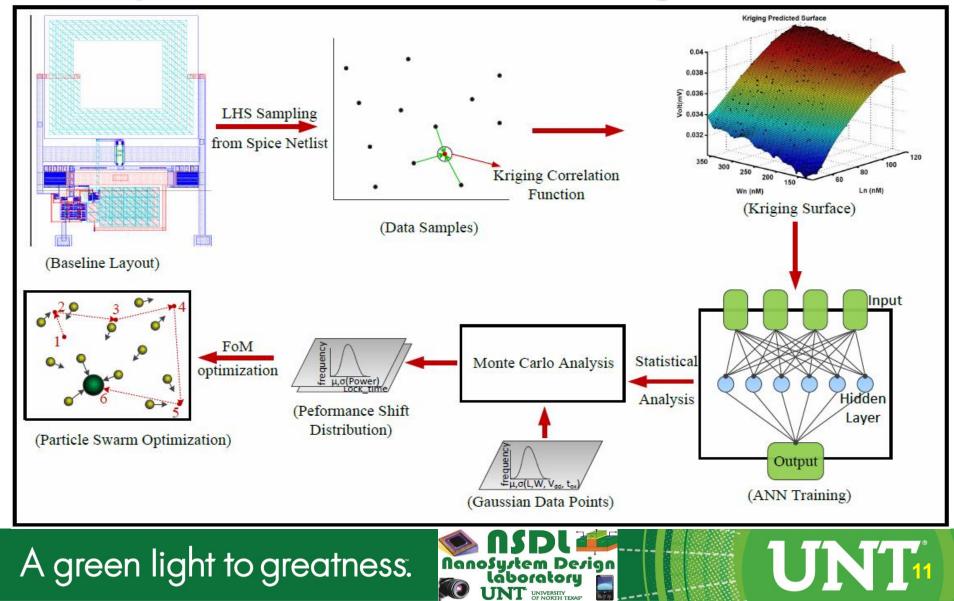

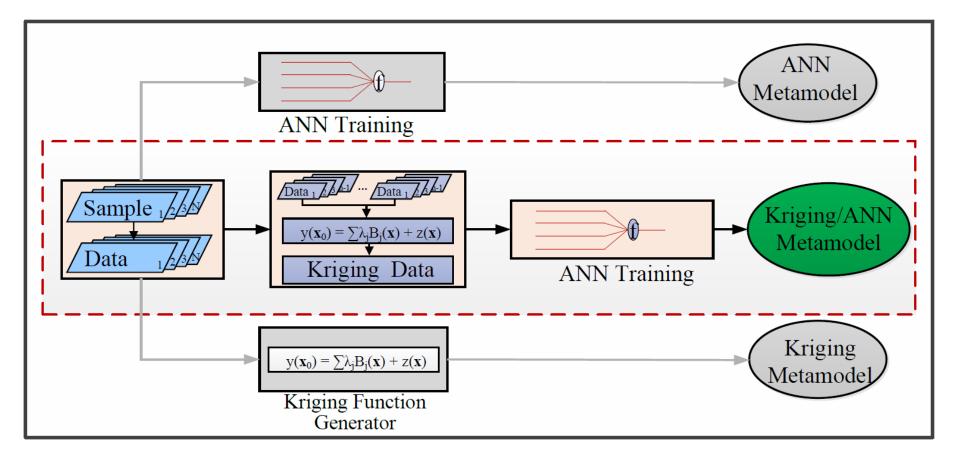

# Proposed Kriging based NN metamodel generation

- Kriging takes into account correlations between the input parameters in performance point prediction

- Hence it is very appealing and lends to high accuracy

- Use of Neural Networks can generate ultra-fast and accurate metamodels

- To ensure time efficiency and accuracy, we present a model that combines Kriging accuracy with NN speed

# **Proposed Kriging based NN metamodel generation flow**

UNIT UNIVERSITY

UNT<sub>17</sub>

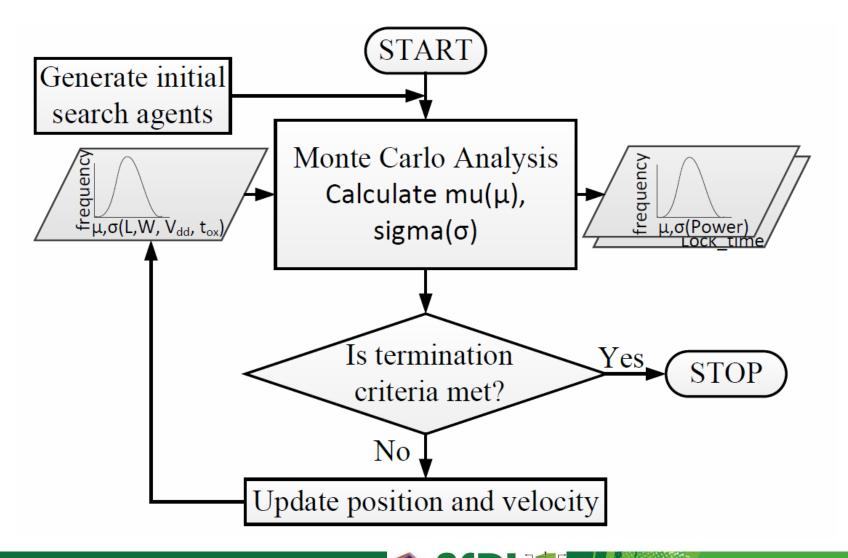

# Particle Swarm Optimization Algorithm

- PSO is a type of evolutionary swarm intelligence algorithm for numerical optimization problems.

- The optimization problem implemented is to minimize power consumption of PLL circuit

- Process aware optimization involves minimizing the mean and standard deviation of optimal power consumption

# Flow Diagram for PSO Algorithm

UNIVERSITY

UΝ

#### **Experimental Steps**

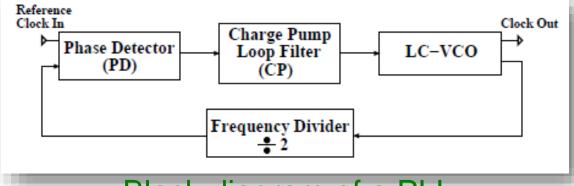

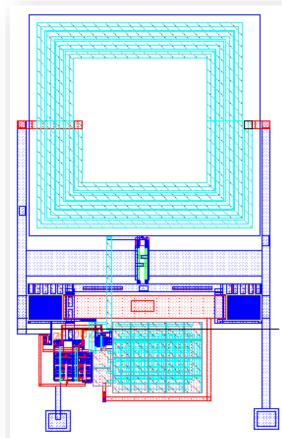

# **Case Study Circuit: 180nm PLL**

Block diagram of a PLL.

- PLL circuit is characterized for frequency, power, vertical and horizontal jitter (for simple phase noise), and locking time.

- Metamodels are created for each FoM from the same sample set.

PLL for 180nm.

21 design parameters used.

#### **Simulation Results**

|                                    |            | SPICE<br>Netlist | Kriging-ANN Metamodel  |              |                       |              |

|------------------------------------|------------|------------------|------------------------|--------------|-----------------------|--------------|

|                                    |            |                  | Before<br>Optimization |              | After<br>Optimization |              |

|                                    |            | Value            | Value                  | Error<br>(%) | Value                 | Error<br>(%) |

| Power (P <sub>PLL</sub> )          | Mean(µ)    | 2.48 mW          | 2.40 mW                | 3.33         | 2.35mW                | 2.08         |

|                                    | St.Dev.(o) | 0.42 mW          | 0.34 mW                | 19.05        | 0.39mW                | 7.14         |

| Frequency (F <sub>PLL</sub> )      | Mean(µ)    | 2.66 GHz         | 2.51 GHz               | 5.64         | 2.78GHz               | 4.51         |

|                                    | St.Dev.(σ) | 10.95 MHz        | 41.93MHz               | 282.92       | 16.92MHz              | 54.52        |

| Locking Time (Lck <sub>PLL</sub> ) | Mean(µ)    | 5.51 µs          | 5.11 µs                | 7.26         | 5.21 µs               | 5.44         |

|                                    | St.Dev.(o) | 0.72 µs          | 0.44 µs                | 38.88        | 0.42 µs               | 41.67        |

| Jitter (J <sub>PLL</sub> )         | Mean(µ)    | 16.80 ns         | 14.69 ns               | 10.25        | 17.72ns               | 5.47         |

|                                    | St.Dev.(o) | 1.32 ps          | 4.50 ps                | 240.91       | 0.33ps                | 75           |

Ng

rign

UNT<sup>22</sup>

#### Conclusions

- Presented a statistical optimization design flow combining Kriging and Neural Network based metamodeling with PSO based algorithm

- The design technique was illustrated through a PLL circuit

- Research will expand for design optimization of various analog blocks in future

UN

# Thank you !!!