# Double Gate FinFET based Mixed-Signal Design: A VCO Case Study

Dhruva Ghai and Garima Thakral Oriental University, Indore, India.

Email: dhruvaghai@orientaluniversity.in, garimathakral@oriental.ac.in

Saraju P. Mohanty

University of North Texas, Denton, TX 76203.

Email: saraju.mohanty@unt.edu.

#### Abstract

- We investigate mixed-signal design for double-gate (DG) FinFET technology using current-starved voltage controlled oscillator (VCO) as a case study.

- Design issues of the DG FinFET-based VCO are presented in a comparative perspective with classical CMOS VCO.

- DG FinFET VCO is analyzed for the figures-of-merit like center frequency, frequency-voltage (f-v) characteristics.

- •Statistical process variation analysis is presented to study the variability in DG FinFET VCO.

- •Surface Models are investigated for the f-v characteristics and width quantization-aware modeling has been presented for the FinFET based VCO. The models can be used for fast design optimization..

#### Introduction

The major advantages of FinFET over CMOS include the following:

- (1) Nearly ideal sub-threshold slope.

- (2) Small intrinsic gate capacitance.

- (3) Smaller junction capacitances.

- (4) Better immunity to SCEs.

- (5) Higher *ION/IOFF* ratio.

- (6)Design flexibility at circuit level with shorted gate (SG) and independent gate (IG) options.

- (7) Higher immunity to SCEs.

- (8) Higher immunity to

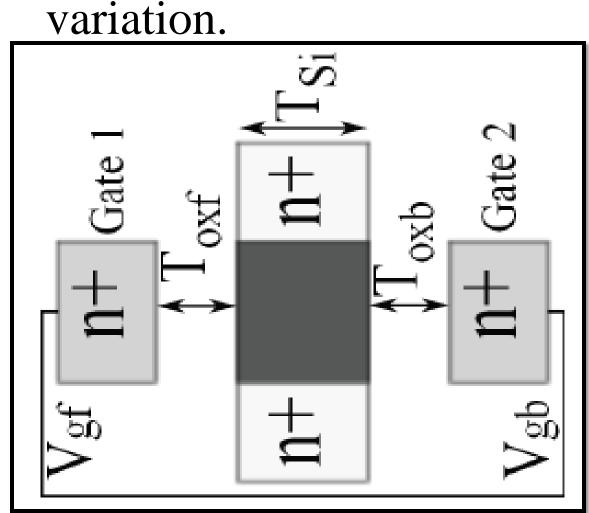

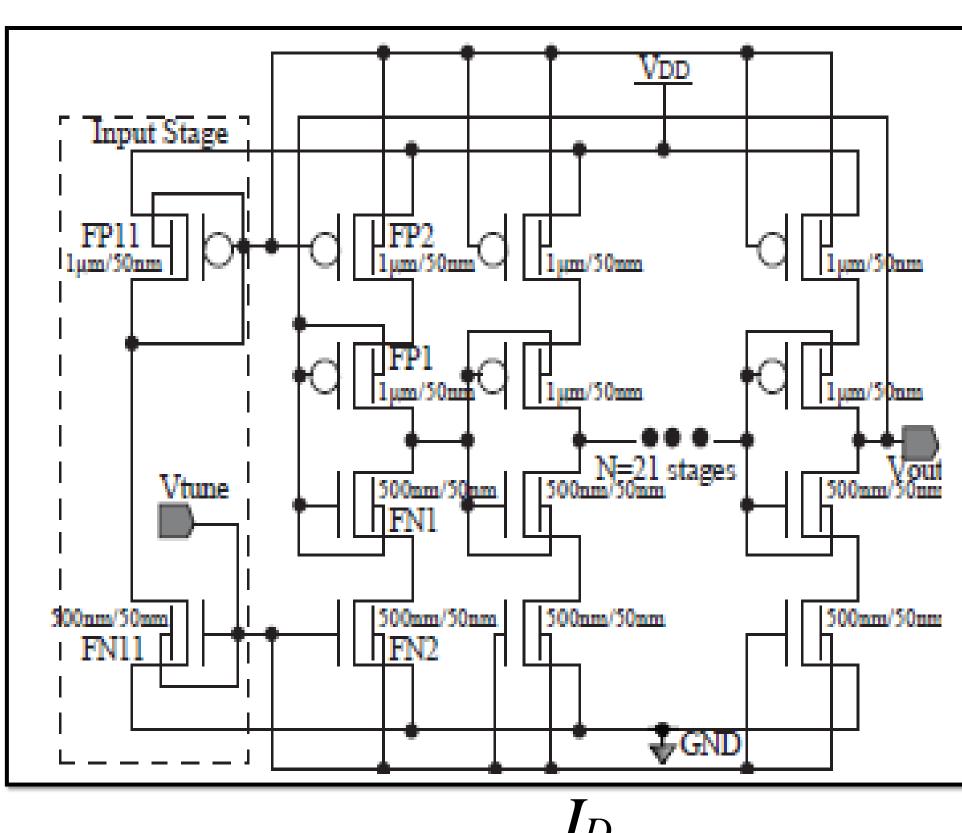

#### DG FinFET VCO

45nm shorted double gate FinFET VCO

$$Freq_{VCO} = \frac{I_D}{(n \times C_t \times V_{DD})}$$

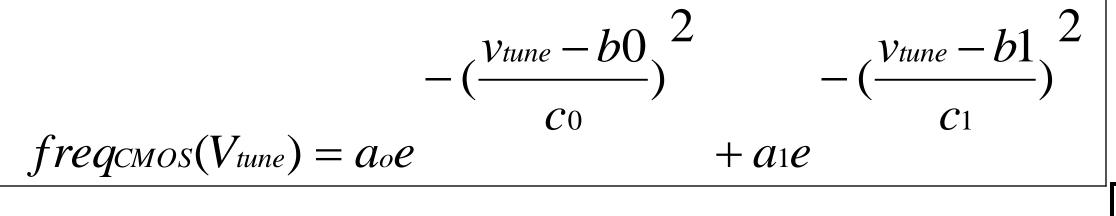

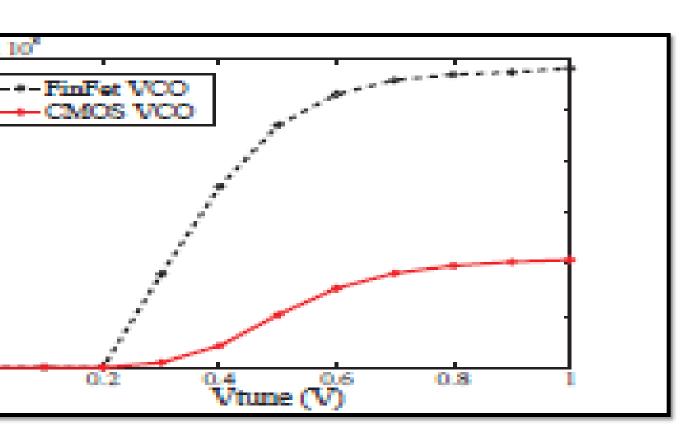

### F-V Characteristics of VCO

Best Fit Equations and Curve

$p_0$

$p^2$

| $a_0$          | 4.126 x 10 <sup>8</sup> |

|----------------|-------------------------|

| $b_0$          | 1.368                   |

| $c_0$          | 1.351                   |

| $\mathbf{a}_1$ | 2.059 x 10 <sup>8</sup> |

| $b_1$          | -0.1438                 |

| $\mathbf{c}_1$ | 0.8269                  |

$$\left| RMSE = \sqrt{\frac{1}{N}} \sum_{i=0}^{N} (freq(V_{tune}^{i}) - (\overline{freq(V_{tune}^{i})})^{2} \right|$$

$$R^{2} = 1 - \frac{\sum_{i=0}^{i=0} (freq(V_{tune}^{i}) - freq(V_{tune}^{i}))^{2}}{\sum_{i=0}^{N} (freq(V_{tune}^{i}) - freq(V_{tune}^{i}))^{2}}$$

## $freq_{FinFET}(V_{tune}) = p_0 + p_1V_{tune} + p_2V^2_{tune} + p_3V^3_{tune}$

$1.1 \times 10^9$

$1.426 \times 10^8$

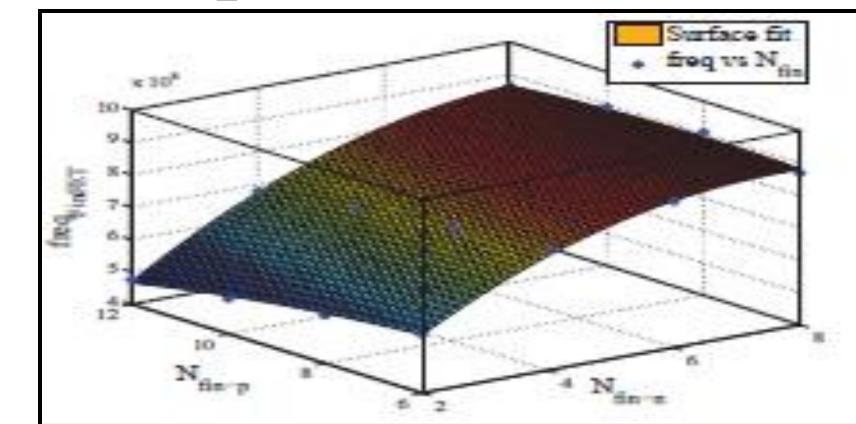

Width-Aware Quantization Modeling

$$freqFinFET = 2H_{fin} \sum_{i,j=0}^{2} pi_j N_{fin-n}^i N_{fin-p}^j$$

$$p_{ij}(freq_{FinFET}) = \begin{bmatrix} 7.9 \times 10^8 & -2.5 \times 10^7 & -8.9 \times 10^8 \\ 1.3 \times 10^8 & 1.4 \times 10^7 & 0 \\ 0 & 0 & 0 \end{bmatrix}$$

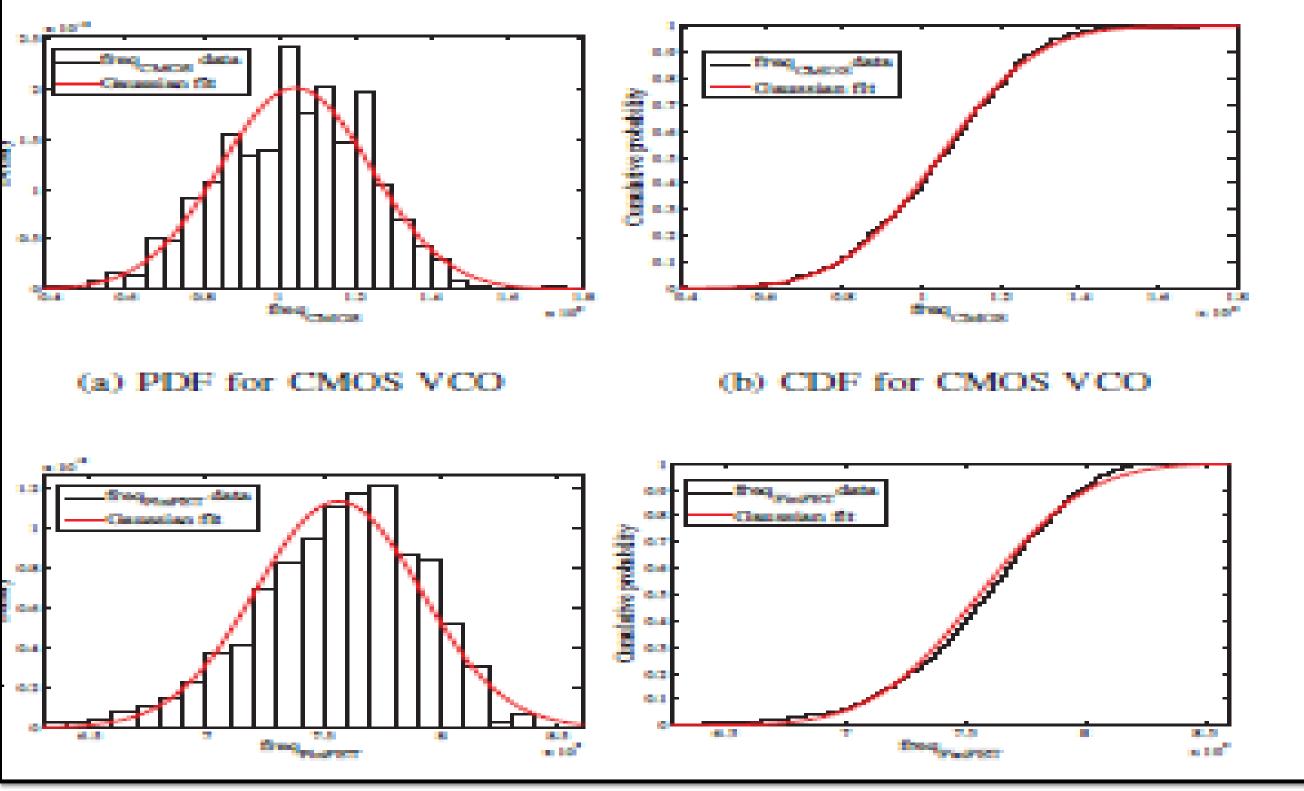

## Statistical Process-Variation Analysis

Statistical Distributed functions for CMOS and FinFET VCO

| Process Variation Data for CMOS and DG FinFET VCO |            |            |                      |  |

|---------------------------------------------------|------------|------------|----------------------|--|

| Measurement                                       | μ          | σ          | $C_v = (\mu/\sigma)$ |  |

| freq <sub>CMOS</sub>                              | 104.37 MHz | 19.812 MHz | 0.1898               |  |

| freq <sub>FinFET</sub>                            | 751.14 MHz | 35.272 MHz | 0.0466               |  |

Chi-square test statistic  $X^2 = \sum_{i=1}^{N} \frac{(O(freq)_i - E(freq)_i)^2}{E(freq)_i}$

#### Conclusion and Future Work

- A comparison is drawn between classical CMOS and DG FinFET based VCO.

- The DG FinFET VCO has a 7× higher center frequency due to smaller intrinsic gate capacitance.

- FinFET VCO shows 4.66% variability due to  $V_{Th}$ fluctuations, as compared to 18.98% variability in the CMOS VCO.

- As part of future research, thermal effects will be examined, as FinFETs suffer from self-heating.

- Width quantization-aware models for power consumption will be developed, and a discrete multiobjective optimization will be performed using FinFET based mixed signal circuits.