# Energy Efficient Nanoelectronic System Design

Saraju P. Mohanty NanoSystem Design Laboratory (NSDL) Dept. of Computer Science and Engineering University of North Texas, Denton, TX 76203, USA. Email: saraju.mohanty@unt.edu

#### **Outline of the Talk**

- Example Consumer Electronic Systems

- Typical Electronic System Components

- The Power Issue: In a Nanoelectronic System

- Options for Energy Efficient System Design

- Conclusions and Future Research

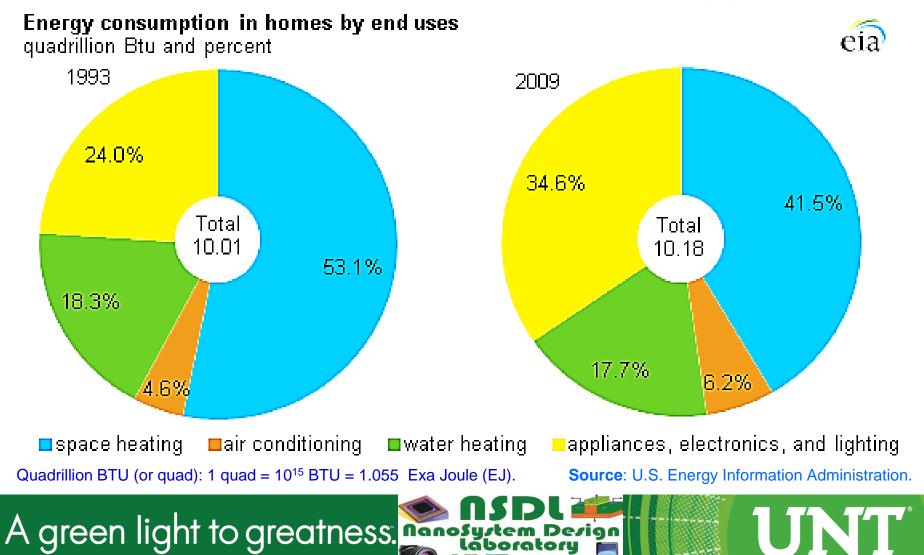

# Consumer Electronics Demand More and More Energy

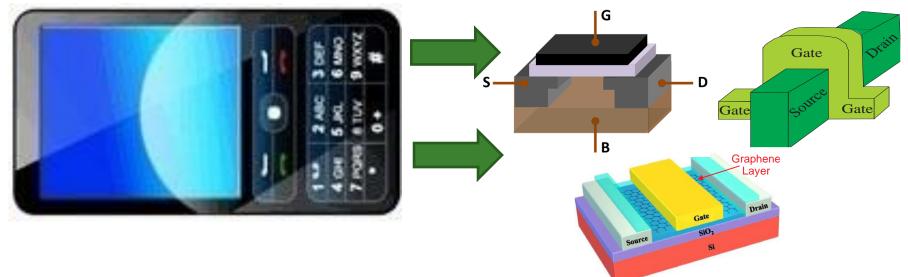

#### **Electronic System: Smart Phone**

**INT**

Smarter ... Faster ... High Throughput ...

> Power Hungry !! Battery Hungry !!

#### Electronic System: Many Others (Same Story)

UNT

Smarter … Faster … High Throughput …

→ Power Hungry !! Battery Hungry !!

#### **Battery Dependency: Not Overstated**

In flight, the airplane is powered by electricity produced by the engine generators. The batteries are part of the multiple layers of redundancy that would ensure power in the extremely unlikely event of a power failure.

A green light to greatness.

One 787 Battery: 12 Cells / 32 V DC

#### Boeing 787's across the globe were grounded.

Source: http://www.newairplane.com

#### Why Energy Efficient Design ? Chip and Packaging system costs cooling costs Noise **Power** Power supply and rail reliability affects Environmental **Battery life** UNT A green light to greatness.

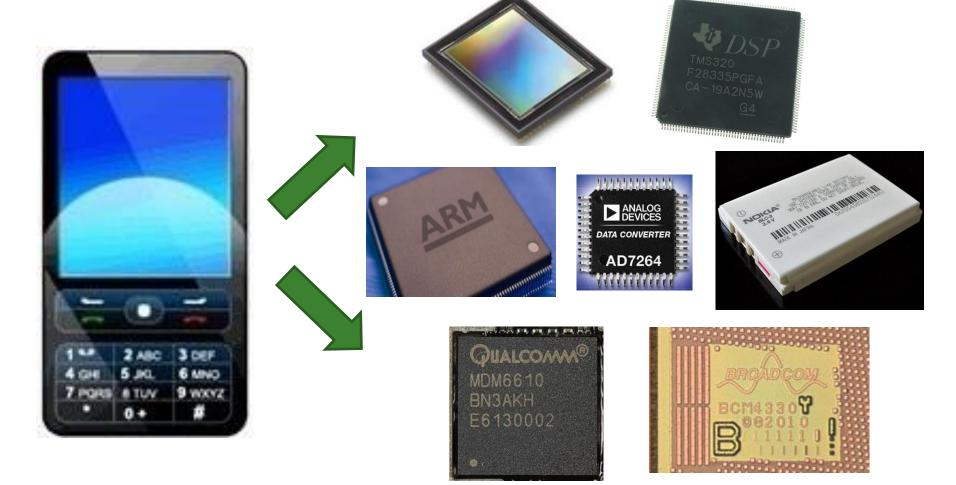

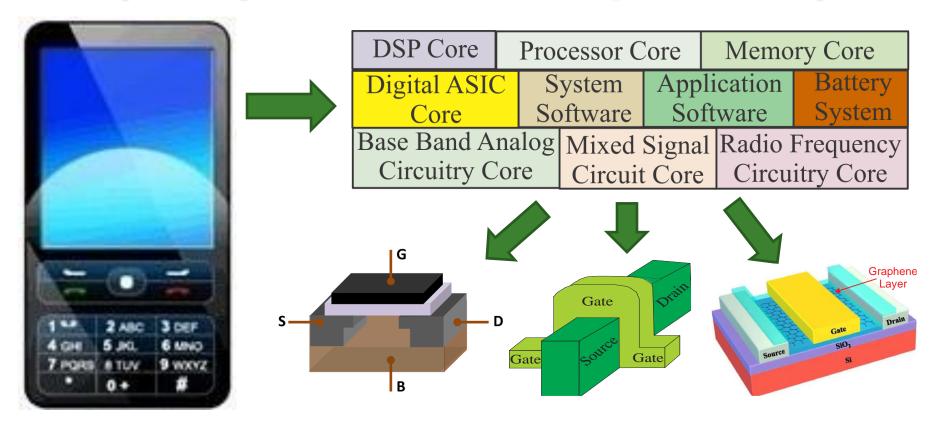

# **A Typical Electronic System**

Consists of several heterogeneous components.

UNÍ

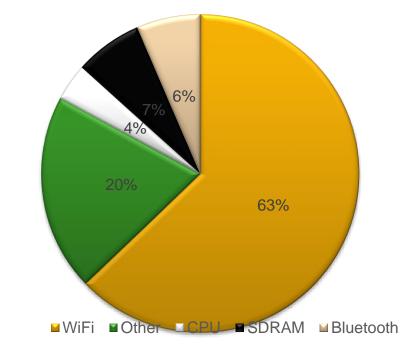

# A Typical Electronic System: Where Energy Consumed??

Power of a Mobile System (in mW)

# Power dissipation breakdown in idle mode of a connected mobile device

Source: Pering MobiSys 2006

## A Typical Nanoelectronic System: (Many Diverse Components)

Components have millions of nanoscale transistors.

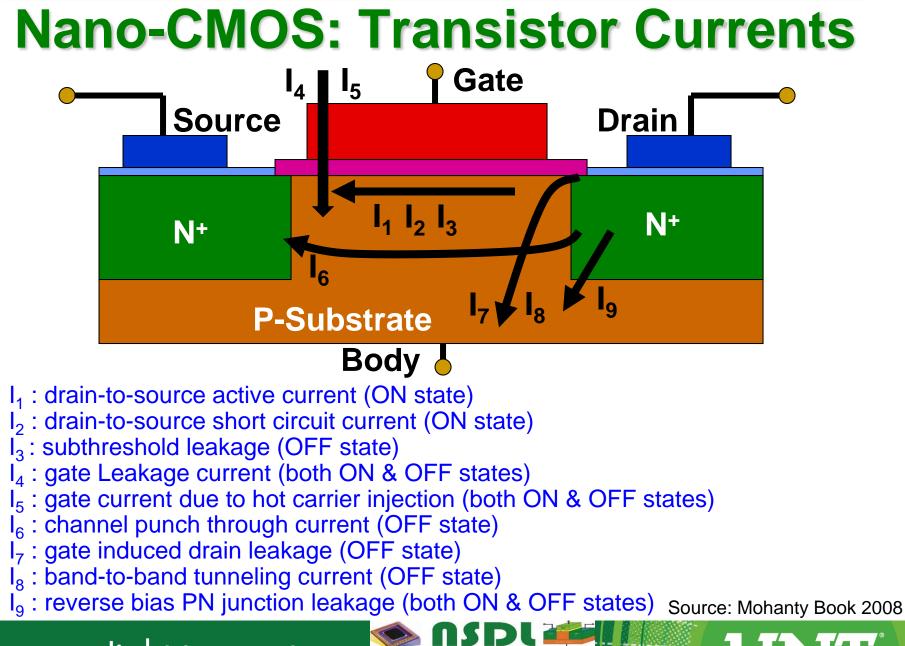

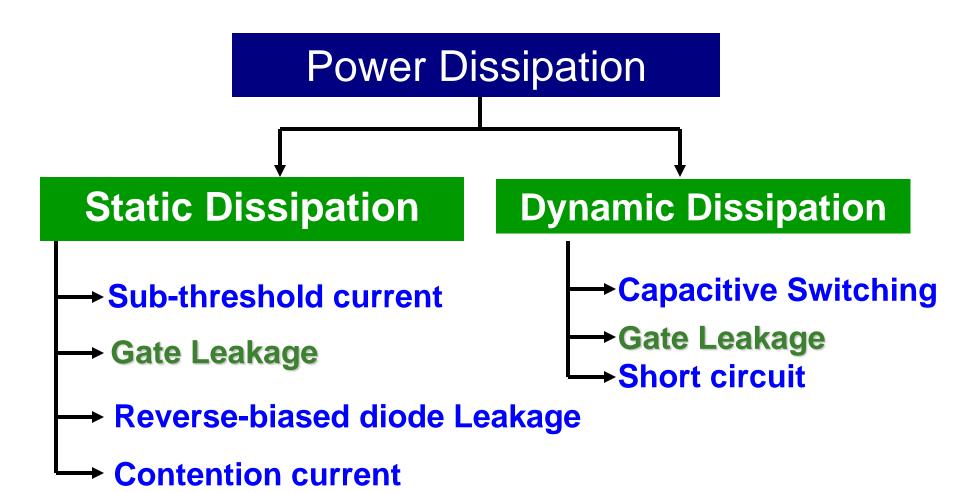

#### **Nano-CMOS: Power Dissipation Types**

A green light to greatness.

Source: Mohanty Book 2008

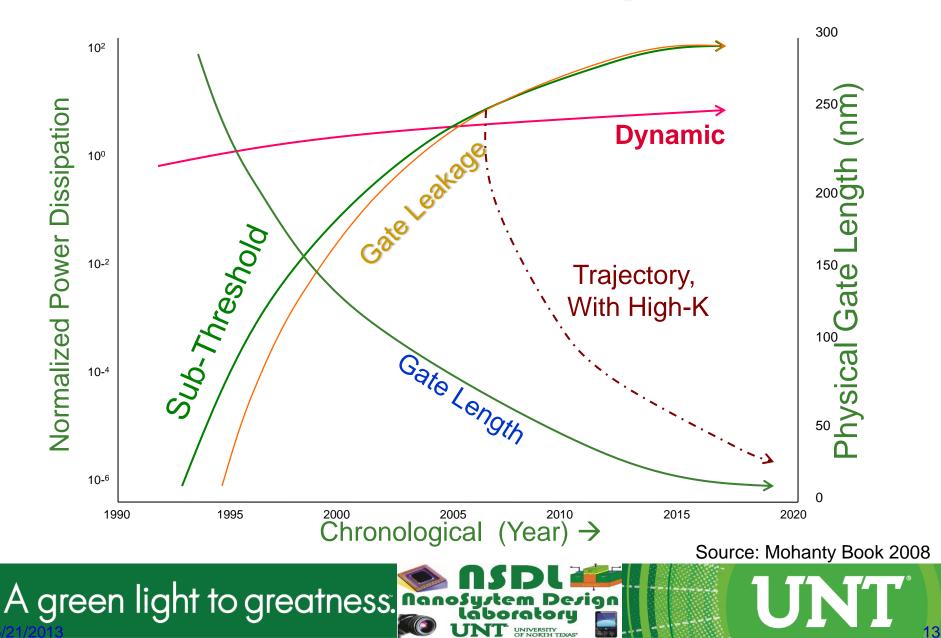

#### **Nano-CMOS: Power Dissipation Trend**

#### A Typical Nanoelectronic System: Research Questions

#### Questions:

How to perform energy-efficient designs.

How to perform high-yield, energy efficient designs.

Bereich und Ber

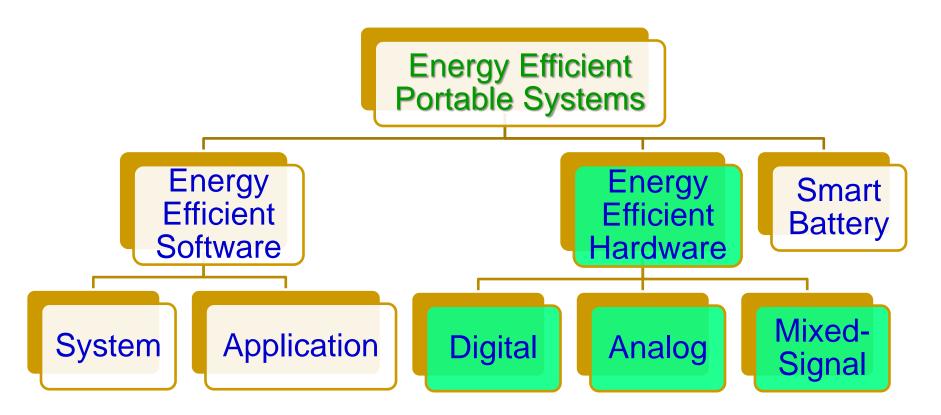

#### **Energy Efficient Nanoelectronic Systems: Possible Solution Fronts**

#### **Energy Efficient Hardware -- 1**

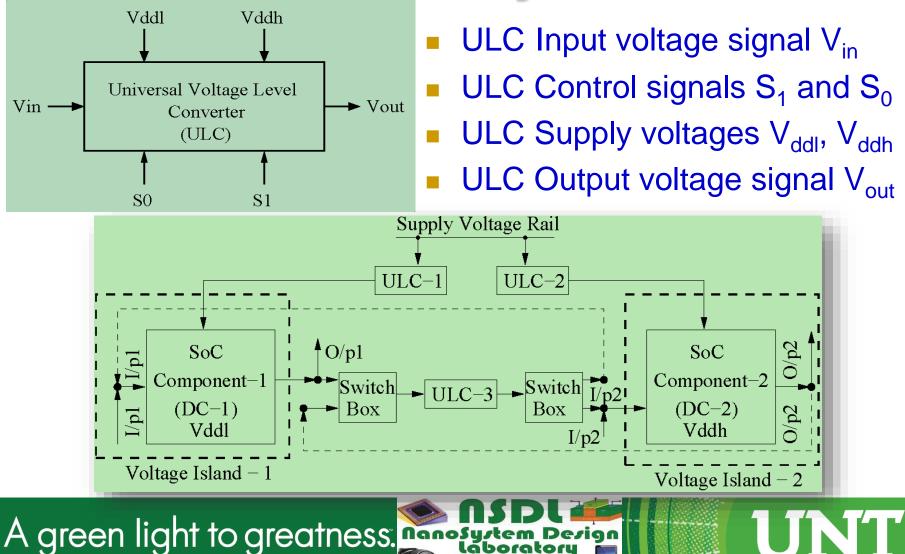

#### Design of an Universal Level Converter for Dynamic Power Management

S. P. Mohanty, E. Kougianos, and O. Okobiah, "Optimal Design of a Dual-Oxide Nano-CMOS Universal Level Converter for Multi-Vdd SoCs", Springer Analog Integrated Circuits and Signal Processing Journal, Vol. 72, No. 2, August 2012, pp. 451--467.

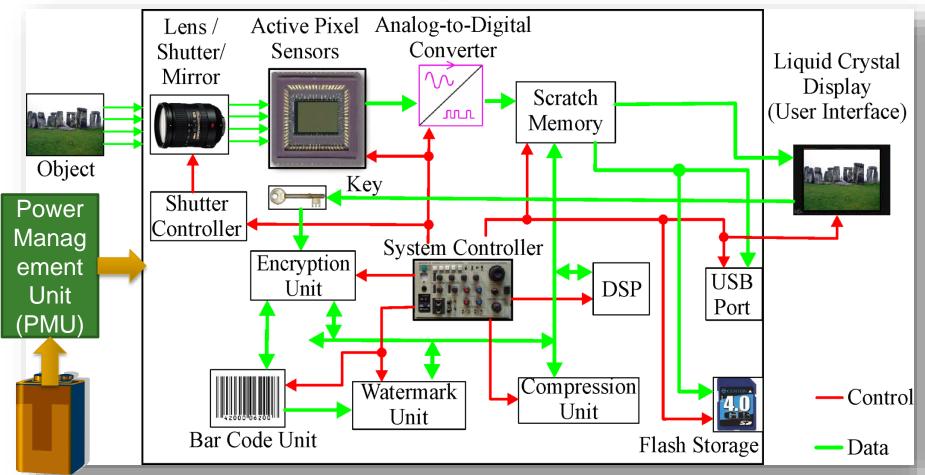

## One Example Electronic System: Secure Digital Camera

UNT

# **Power Management Unit (PMU)**

- Manages the power distribution to the various subsystems to optimize energy consumption.

- Has built-in timers that put the different components to "sleep" or "wake-up".

- The heart of PMU is a bank of Universal Voltage-Level Converters (ULCs).

- ULC sends different operating voltages to various subsystems and facilitates reconfigurability for power management.

#### Universal Voltage-Level Converter: Use in a System

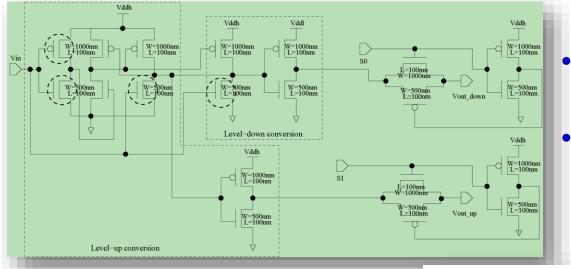

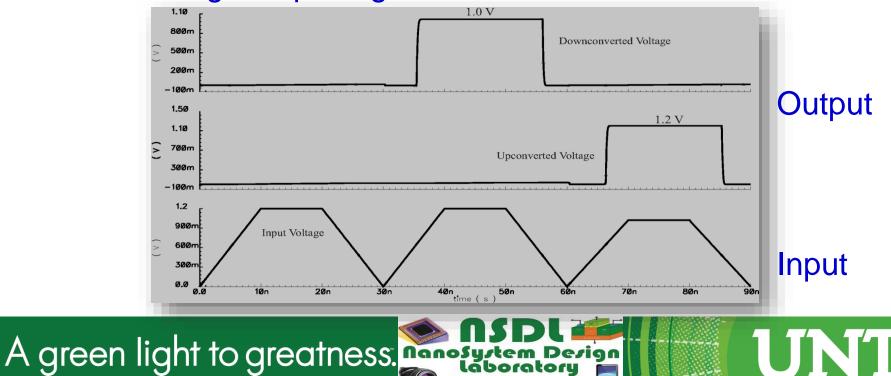

# Universal Voltage-Level Converter: One Topology

- 20 transistor area efficient design.

- Energy hungry transistors are circled.

- Energy hungry transistors have thicker oxide.

- 90nm CMOS dual-oxide physical design of ULC.

#### Universal Voltage-Level Converter: Operations

#### Operations of the ULC:

- Level-up conversion

- Level-down conversion

- Blocking of input signal

| Select Signal |   | Type of Operation |

|---------------|---|-------------------|

| 0             | 0 | Block Signal      |

| 0             | 1 | Up Conversion     |

| 1             | 0 | Down Conversion   |

#### Universal Voltage-Level Converter: Has Minimal Overhead

| Designs          | Technology<br>(nm) | Power        | Delay    | Conversion                     | Design<br>Approach                          |

|------------------|--------------------|--------------|----------|--------------------------------|---------------------------------------------|

| Ishihara<br>2004 | 130nm              |              | 127 ps   | Level-up and down              | Level<br>converting flip<br>flops           |

| Yu<br>2001       | 350nm              | 220.57<br>μW |          | Level-up                       | SDCVS                                       |

| Sadeghi<br>2006  | 100nm              | 10 µW        | 1 ns     | Level-up                       | Pass transistor<br>and Keeper<br>transistor |

| Our ULC          | 90 nm              | 12.26<br>μW  | 113.8 ps | Level-<br>up/down and<br>block | All conversion<br>types and<br>Programmable |

A green light to greatness.

UNT

#### Energy Efficient Hardware -- 2

- Design of Energy-Efficient Phase-Locked Loop (PLL) for Clock Generation

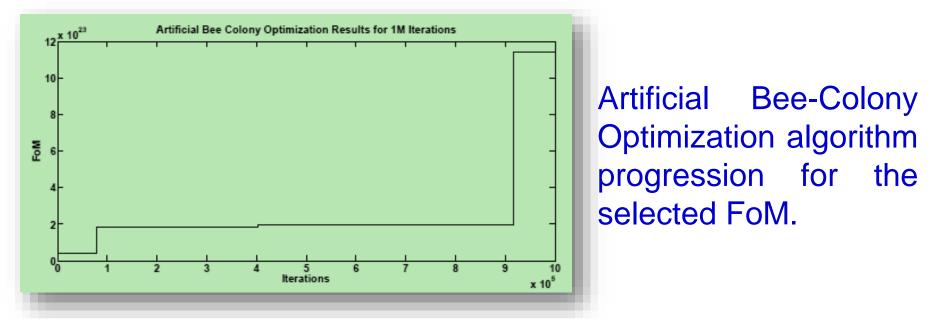

- O. Garitselov, S. P. Mohanty, and E. Kougianos, "Accurate Polynomial Metamodeling-Based Ultra-Fast Bee Colony Optimization of a Nano-CMOS PLL", *Journal of Low Power Electronics*, Volume 8, Issue 3, June, 2012, pp. 317--328.

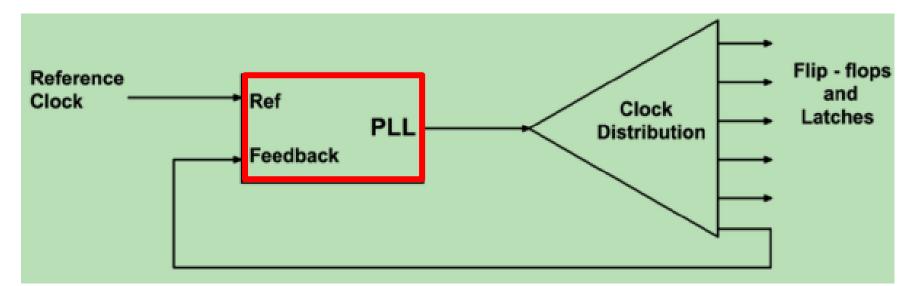

## **Phase Locked Loop: Application**

#### PLLs are everywhere.

- PLLs drive clock distribution of a synchronous system.

- Sequential elements like Flip-Flop, Latches, and Registers need clock.

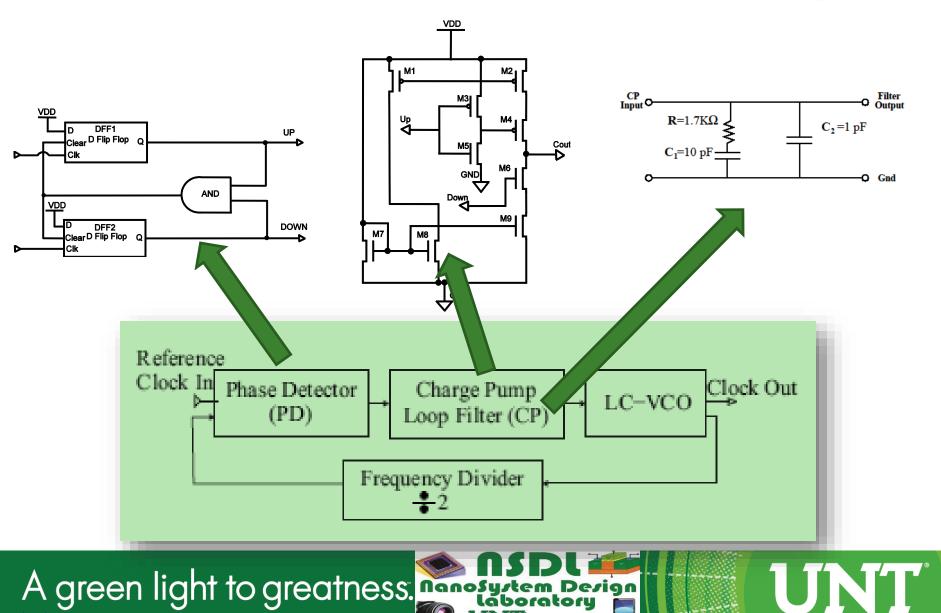

#### Phase Locked Loop: Block Diagram

25

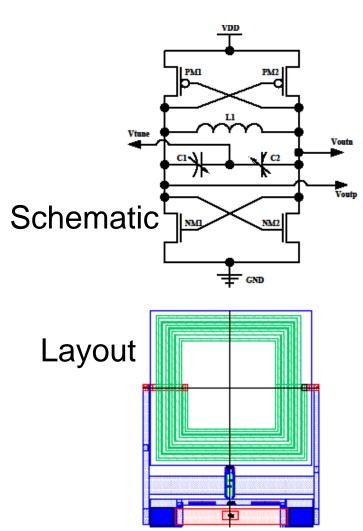

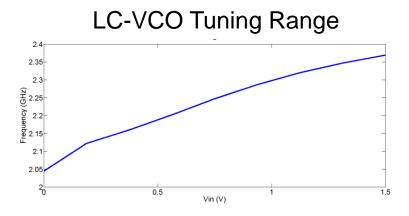

# PLL Component: 180nm LC-VCO

LC-VCO oscillations are based on the sizes of L1 and C1=C2 varactors.

#### **Optimization of the PLL**

#### PLL parameters with constraints

#### and optimized values.

| Circuit        | Parameter   | Min    | Max     | Optimal    |

|----------------|-------------|--------|---------|------------|

|                |             | (m)    | (m)     | Value (m)  |

|                | $W_{ppd1}$  | 400n   | $2\mu$  | $1.66\mu$  |

|                | $W_{npd1}$  | 400n   | $2\mu$  | $1.11\mu$  |

| Phase Detector | $W_{ppd2}$  | 400n   | $2\mu$  | 784n       |

| Thase Detector | $W_{npd2}$  | 400n   | $2\mu$  | 689n       |

|                | $W_{ppd3}$  | 400n   | $2\mu$  | $1.54\mu$  |

|                | $W_{npd3}$  | 400n   | $2\mu$  | 737n       |

|                | $W_{nCP1}$  | 400n   | $2\mu$  | $1.24\mu$  |

| Charge Pump    | $W_{pCP1}$  | 400n   | $2\mu$  | $1.35\mu$  |

| charge r amp   | $W_{nCP2}$  | $1\mu$ | $4\mu$  | $1.35\mu$  |

|                | $W_{pCP2}$  | $1\mu$ | $4\mu$  | $2.88\mu$  |

| LC-VCO         | $W_{nLC}$   | 3μ     | $20\mu$ | $18.62\mu$ |

| 20,000         | $W_{pLC}$   | $6\mu$ | $40\mu$ | $37.48\mu$ |

|                | $W_{p1Div}$ | 400n   | $2\mu$  | $1.65\mu$  |

|                | $W_{p2Div}$ | 400n   | $2\mu$  | $1.54\mu$  |

|                | $W_{p3Div}$ | 400n   | $2\mu$  | $1.38\mu$  |

|                | $W_{p4Div}$ | 400n   | $2\mu$  | $1.96\mu$  |

| Divider        | $W_{n1Div}$ | 400n   | $2\mu$  | $1.09\mu$  |

|                | $W_{n2Div}$ | 400n   | $2\mu$  | $1.17\mu$  |

|                | $W_{n3Div}$ | 400n   | $2\mu$  | $1.29\mu$  |

|                | $W_{n4Div}$ | 400n   | $2\mu$  | $1.95\mu$  |

|                | $W_{n5Div}$ | 400n   | $2\mu$  | 536n       |

- An exhaustive search of the design space of 21 parameters with 10 intervals per parameter requires 10<sup>21</sup> simulations.

- Time savings are enormous: ~10<sup>20</sup>x.

- This can lead to reduction of design effort and chip cost.

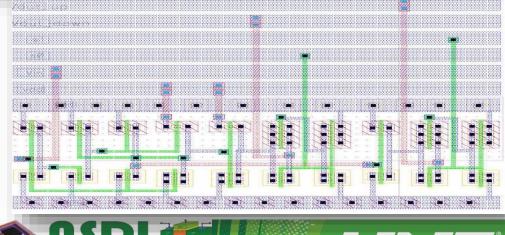

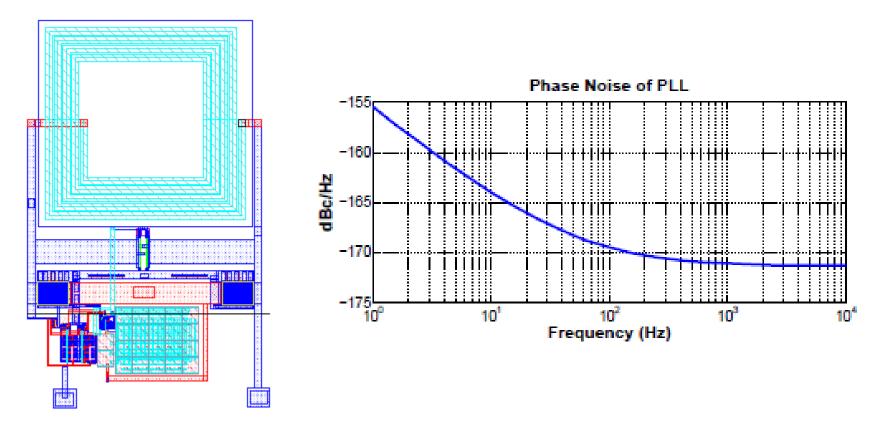

#### **Complete PLL : 180nm**

PLL physical design for 180nm

#### **Optimization of the PLL ...**

#### **Power and Jitter Results of the PLL**

| Metric            | Before<br>Optimization | After<br>Optimization | Improvement  |

|-------------------|------------------------|-----------------------|--------------|

| Power             | 9.29 mW                | 0.87 mW               | 90.6%        |

| Jitter Vertical   | 168.35µV               | 3.28 nV               | $\sim 100\%$ |

| Jitter Horizontal | 189 ps                 | 180 ps                | 4.8%         |

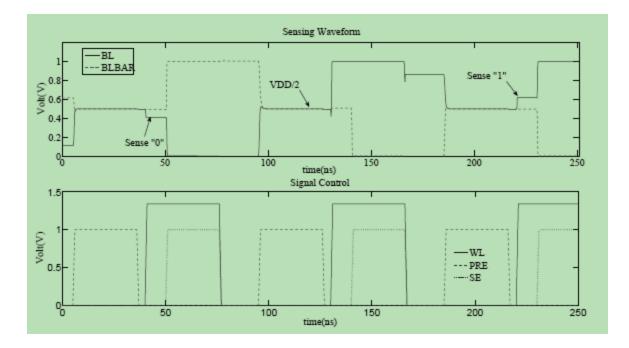

#### **Energy Efficient Hardware -- 3**

#### Design of Energy-Efficient Sense Amplifier for Memory

O. Okobiah, S. P. Mohanty, E. Kougianos, and M. Poolakkaparambil, "Towards Robust Nano-CMOS Sense Amplifier Design: A Dual-Threshold versus Dual-Oxide Perspective", in *Proceedings of the 21st ACM/IEEE Great Lakes Symposium on VLSI (GLSVLSI)*, 145--150, 2011.

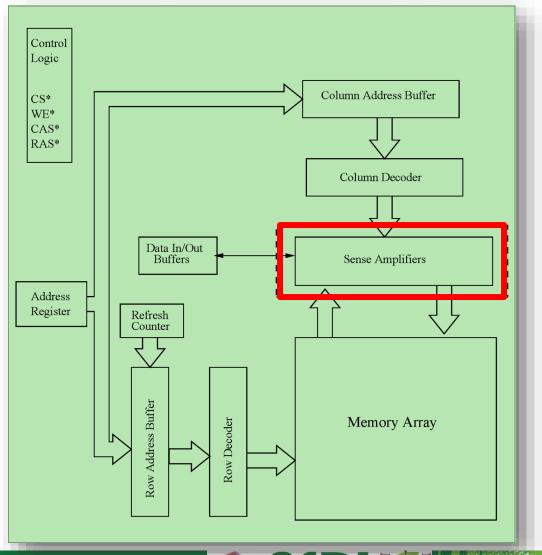

#### **Sense Amplifier : Application**

UNIVERSITY

UNT

31

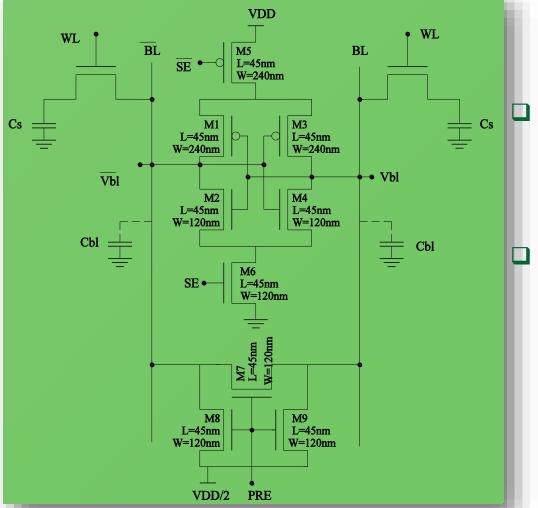

#### **Functional Design of Sense Amplifier**

M1, M3, M2 and M4 form cross-coupled inverters.

M7, M8 and M9 form the precharge circuit

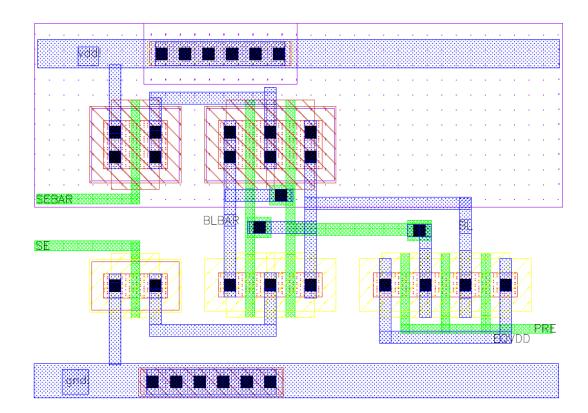

#### **45nm Sense Amplifier Layout**

□  $L_n = 45nm$ □  $L_p = 45nm$ □  $W_n = 120nm$ □  $W_p = 240nm$

UNT

#### **45nm Sense Amplifier: Simulation**

| Design    | Precharge<br>time (ns) | Sense delay<br>(ns) | Power,<br>(μW) | Sense Margin<br>(mV) | Area (μm²) |

|-----------|------------------------|---------------------|----------------|----------------------|------------|

| Schematic | 10.31                  | 1.79                | 1.84           | 26.91                | -          |

| Layout    | 10.40                  | 1.91                | 1.88           | 26.86                | 6.045      |

IININ/EPCITS

34

#### 45nm Sense Amplifier: Characterization of Optimal Design

| Circuit              | Precharge<br>Time | Power<br>Dissipation | Sense Delay | Sense Margin |

|----------------------|-------------------|----------------------|-------------|--------------|

| Schematic            | 18.024 ns         | 1.166 µW             | 7.460 ns    | 29.331 mV    |

| Layout               | 18.20 ns          | 1.175 μW             | 7.45 ns     | 29.256 mV    |

| Dual-V <sub>th</sub> | 6.61 ns           | 0.941 µW             | 3.476 ns    | 40.851 mV    |

| Dual-T <sub>ox</sub> | 6.596 ns          | 0.895 µW             | 3.464 ns    | 40.77 mV     |

UNT

# **Sense Amplifier: Comparison**

| Research                 | Parameter                             | Feature                | Approach                | Result Improvement                                             |

|--------------------------|---------------------------------------|------------------------|-------------------------|----------------------------------------------------------------|

| Chow<br>MWSCAS-2007      | C <sub>BL</sub>                       | Sense<br>Speed         | Spice<br>simulations    | Sense speed – 40%                                              |

| Laurent<br>TCASI 2002    | $C_{BL}$ , $V_{th}$ , $\beta$         | Signal<br>Margin       | Spice<br>Simulations    | -                                                              |

| Choudhary<br>ISVLSI 2009 | V <sub>th</sub> , L, W                | Yield                  | Monte Carlo<br>analysis | Improved Yield                                                 |

| Singh<br>TVLSI 2004      |                                       | SE rise time           | Spice<br>simulations    | Eliminated offset voltage                                      |

| Our Sense<br>Amplifier   | Dual-V <sub>th,</sub> T <sub>ox</sub> | Process<br>variability | Optimization            | Sense delay – 54%<br>Sense margin – 40%<br>Average Power – 24% |

#### Conclusions

- 35% of total energy in USA is consumed by electronics.

- Battery dependency is an critical constraint for portable systems.

- Energy efficient hardware, software at the same time better battery design needed for effective solutions.

- Smartphones need to have energy-efficient analog and RF components as WiFi and GSM communication consume significant portion of battery life.

- Energy-efficient level converters can perform better power management.

- 180 nm PLL design example consumed 90% less power.

- 45nm sense amplifier example consumed 24% less power.

# hank You

Slides Available at: http://www.cse.unt.edu/~smohanty