#### LOW POWER NANOSCALE BUFFER MANAGEMENT FOR NETWORK ON CHIP ROUTERS

- Suman K. Mandal, Texas A&M University

- Ron Denton, Texas A&M University

- □ Saraju P. Mohanty, University of North Texas

- Rabi N. Mahapatra, Texas A&M University

Contact: skmandal@cse.tamu.edu

Acknowledgement: This research is supported in part by NSF award number 0509483 and 0854182.

# Talk Outline

- Introduction and Motivation

- Contributions

- Related Prior Research

- Router Architecture

- Block-Level Power Management

- Low Power SRAM Buffer

- Flit-Level Power Management

- Conclusions

GLSVLSI 2010

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

# Introduction: Why NoC?

- Network on Chip

Next Gen Interconnect

GALS Approach

- Advantages

- High Bandwidth

- Scalable

- Extensible

- Disadvantages

- Power Hungry

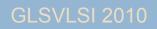

48 Core Chip from Intel Uses 24 Node Mesh Network on Chip

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

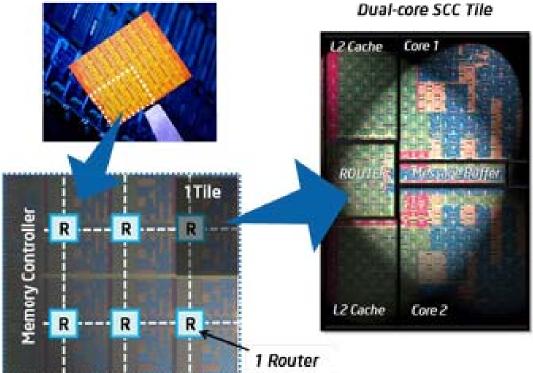

# **NoC: Structure**

- NoC consists of routers, links and corenetwork interfaces (CNI).

- Routers are responsible for routing communication between the different parts.

- The CNI provides an interface for the IP cores to the NoC.

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

Flit

Routing

Flit

Virtual Channel Allocation

Flit

Switch Arbitration

17 May 2010

Flit

Flit

# **NoC: Salient Features**

- 6

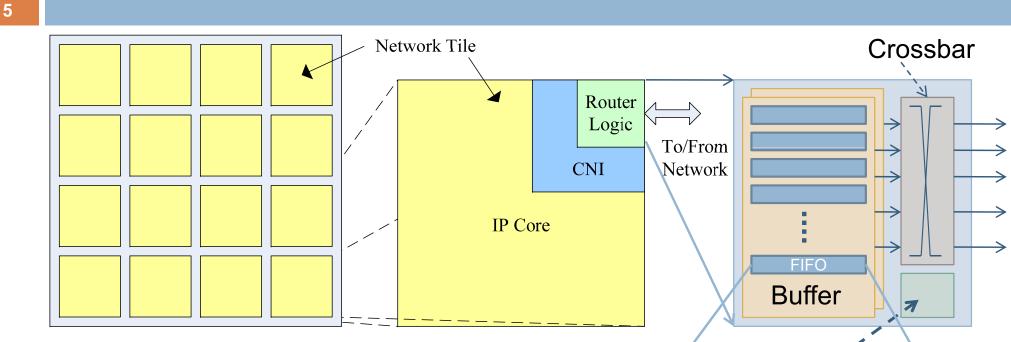

- Buffer size, type and allocation policy play an important role in the performance and efficiency of a NoC router.

- Buffers can consume as much as up to 79% of NoC router power.

- Buffer utilization in NoC router is dependent on network congestion.

- Depending on communication pattern of an application a buffer utilization of a router varies over time.

#### **Chip Power Breakdown**

GLSVLSI 2010

7

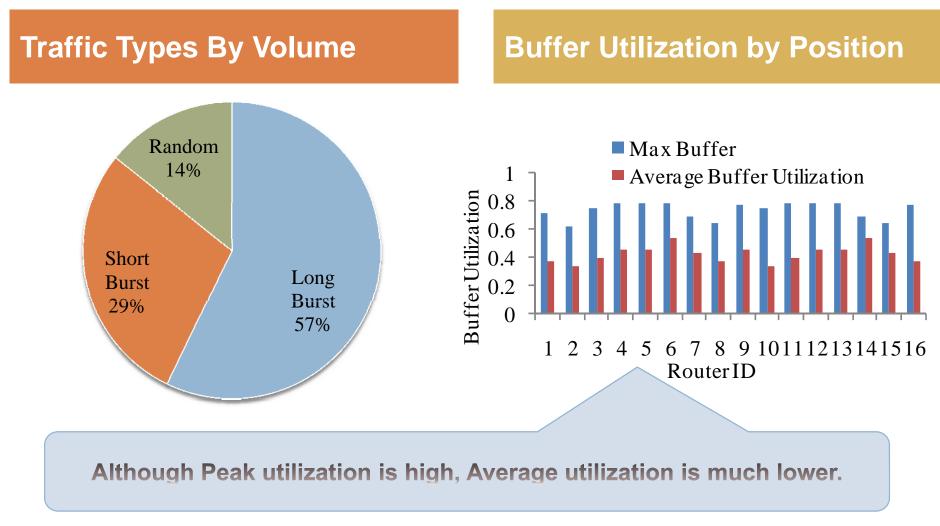

# **Traffic and Buffer Utilization**

GLSVLSI 2010

# **Types of NoC Buffers**

- 9

- □ First-In-First-Out (FIFO) registers.

- Static random access memory (SRAM) based buffers.

GLSVLSI 2010

# **NoC Buffers: SRAM Advantages**

Nanoscale SRAM buffers are suitable for NoC router design because of their speed, density and reliability.

# Motivation for this Research

- 11

- Efficient buffer management is necessary to ensure high performance and low power.

- Power dissipation characteristics of nanoscale SRAMs are unique and hence traditional low power design techniques are not sufficient to ensure minimum power operation.

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

# Idea!

- Can the knowledge of traffic be utilized to minimize the buffer requirement?

- Yes, because burst modes can be detected easily.

- How to minimize the buffer requirement?

By dynamically resizing the buffers to required size.

GLSVLSI 2010

# The Contributions

- A feedback controlled block-level buffer management is proposed for power management.

- An adaptive controller for efficient flit-level power management is proposed.

- Both power management techniques are thoroughly evaluated for performance.

- Results outperform static allocation by 21% increase in throughput and 20% reduction in energy consumption.

GLSVLSI 2010

14

GLSVLSI 2010

## **Prior Research**

- 16

- There have been significant research on router buffer power management for low power.

- Both circuit level and system level techniques have been proposed for NoC power management.

- Detail discussion on existing research is available in Simunic-DATE2002, Banerjee-NoCSymposium2007, Ogras-CODES2005.

## Prior Research ...

#### □ Zhang et al. GLSVLSI 2009:

- A centralized buffer management to achieve enhanced buffer utilization.

- Demonstrated a 50% decrease in total buffer requirement in their router.

- Did not provide an active power management strategy.

# Prior Research ...

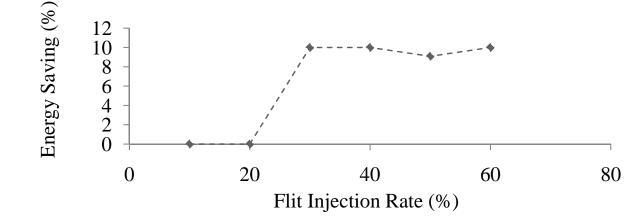

#### □ Wang et al. DATE 2008:

- Proposed a zero-efficient design for router buffers that optimizes the circuit level design of router buffer.

- Basis of their research is predominance of zeros in the NoC traffic.

- This is primarily a circuit level work under the assumption of high zero density and does not necessarily fare well when there is majority of one.

- They do not consider any system-level information or active power management technique to adapt to the dynamic nature of the traffic.

GLSVLSI 2010

GLSVLSI 2010

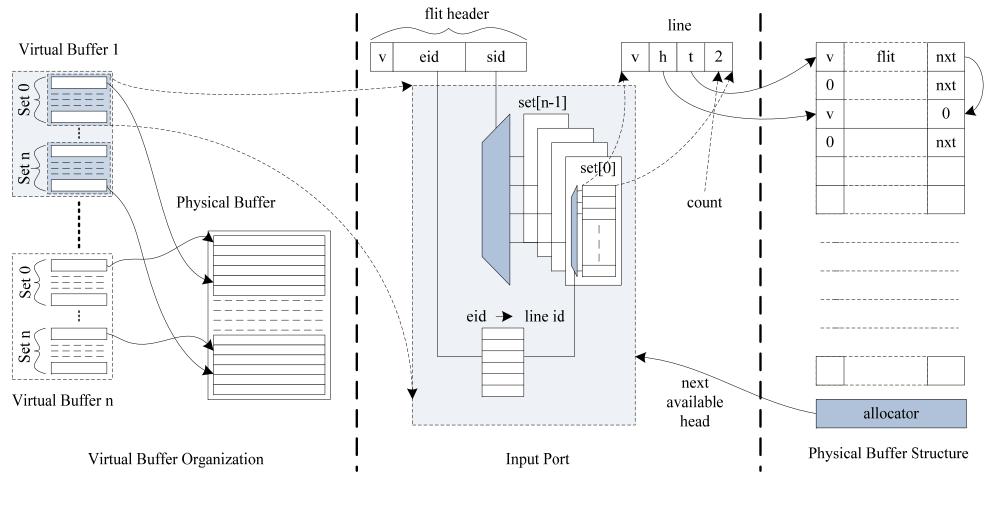

# **Router Architecture: Features**

- The proposed buffer design is suitable for routers with centralized buffer management.

- To effectively utilize the central buffer design a concept of virtual buffer is introduced.

- Queue management is performed in the physical buffer.

- A concept of set and line is introduced for allocating buffer.

GLSVLSI 2010

# Router Architecture: Features ...

- The virtual buffers allow independent management of the central buffer structure.

- The physical buffer is managed centrally and each virtual buffer may or may not be mapped to a physical buffer.

- To be able to effectively perform power management using power gating the buffer is grouped in blocks.

21

#### **Central Buffer Router Architecture**

22

GLSVLSI 2010

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

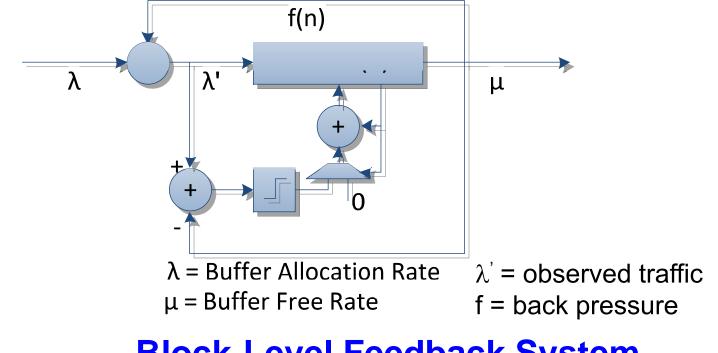

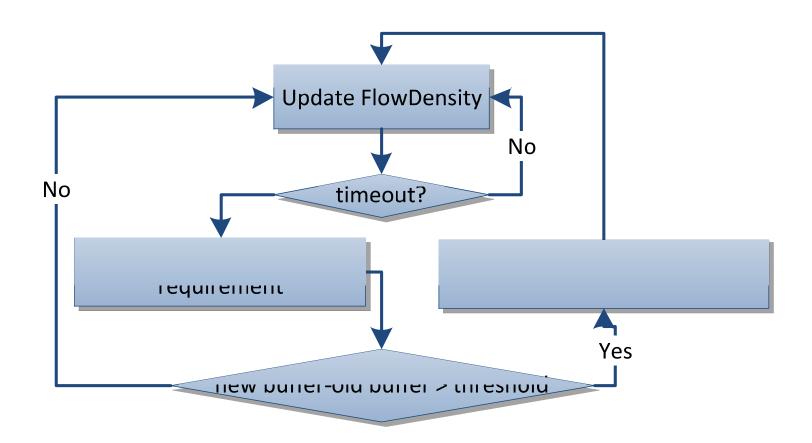

## **Block-Level Power Management**

24

- Traffic flow is modeled as a feedback loop.

- □ The buffer size is controlled by a threshold function.

#### **Block-Level Feedback System**

GLSVLSI 2010

#### **Controller FSM**

GLSVLSI 2010

#### How to Resize Buffer

#### Solution

- Organize Buffer in blocks

- Turn of un-used blocks

#### Challenge

Central Buffer Router is needed

GLSVLSI 2010

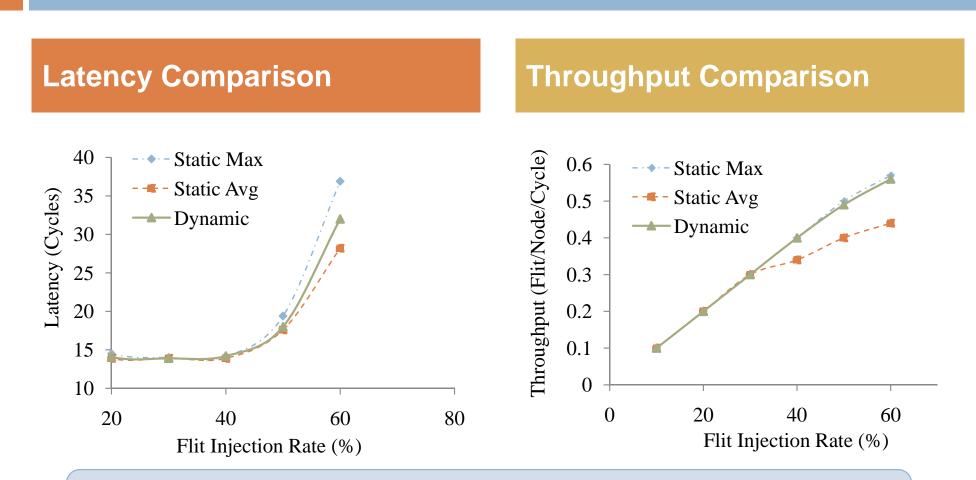

## **Performance Results**

**21%** Throughput Improvement at negligible loss of latency

GLSVLSI 2010

# **Energy Savings**

**10% Energy Savings Compared to Static Buffer**

GLSVLSI 2010

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

#### 7-Transistor Low Leakage SRAM

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

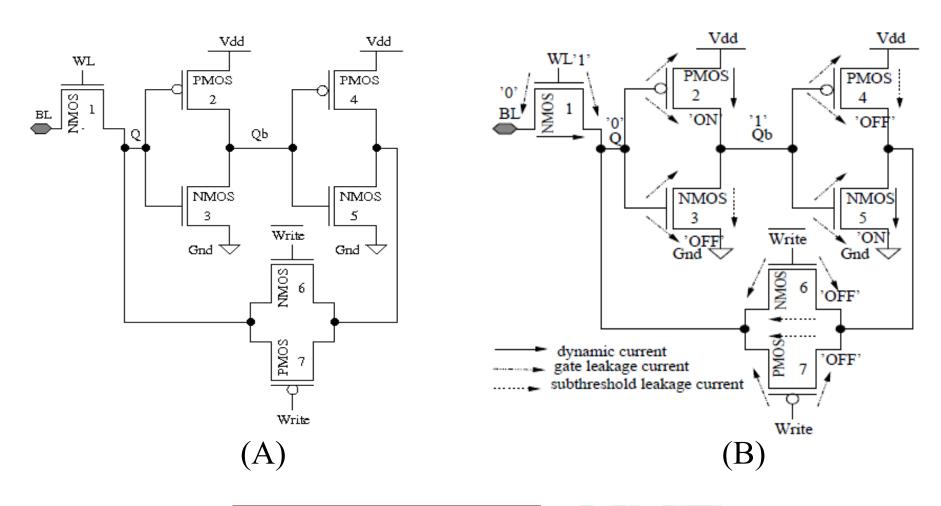

#### **SRAM Power Model**

GLSVLSI 2010

Store 0

17 May 2010

2.9nW

17.2nW

## Idea!

# Encode flits so that the storage is least energy consuming Done by utilizing system level information about flit content

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

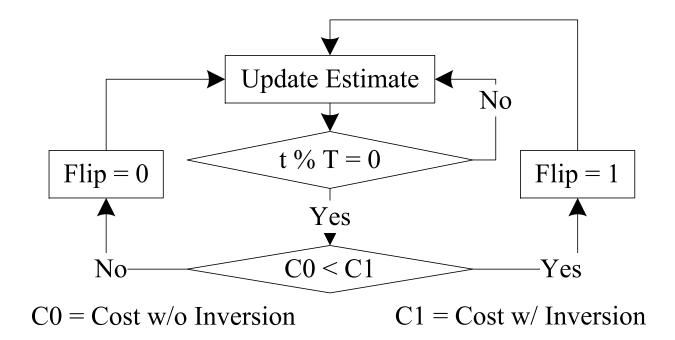

### Flit-Level Power Management: Approach

- A dynamic encoding technique is applied per flit to for further energy efficiency.

- Invert flits before writing to buffer if resulting energy consumption is less.

- Use an adaptive controller to trigger inversion.

34

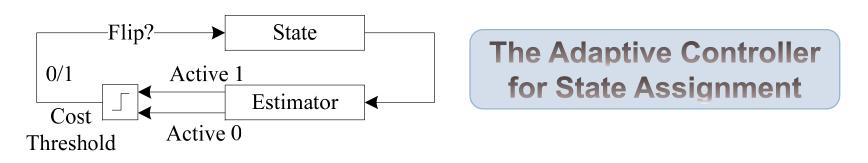

# The Adaptive Controller

- 35

- Any flit can be stored in one of the three states: Active 0, Active 1 or Sleep.

- A linear adaptive control mechanism is designed to assign the flit storage states dynamically.

- A simple estimator is designed for low overhead.

- Flits are marked to be '1-dense' by adding a bit to header.

- A simple estimate is the frequency of this bit being set.

GLSVLSI 2010

#### **The Adaptive Controller**

36

**Controller FSM**

GLSVLSI 2010

UNIVERSITY OF NORTH TEXAS Discover the power of ideas

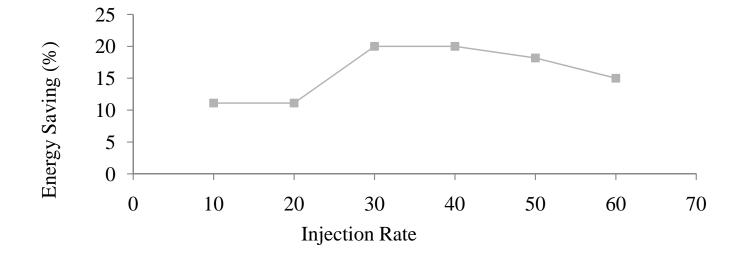

# **Energy Savings**

20% Energy Savings Compared to Generic Design

GLSVLSI 2010

17 May 2010

GLSVLSI 2010

#### Conclusions

- A novel low power nano-CMOS buffer design was presented.

- Combined block and flit level power management is performed for throughput and power efficiency.

- Proposed technique utilizes system level information for effective power management of router buffer.

- Experimental evaluation have demonstrated the proposed design to be outperforming static buffer allocation by 21% in terms of throughput while consuming up to 20% less power.

17 May 2010

GLSVLSI 2010