Parasitic Aware Process Variation Tolerant Voltage Controlled Oscillator (VCO) Design

Dhruva Ghai, Saraju P. Mohanty, and Elias Kougianos VLSI Design and CAD Laboratory (VDCL) Dept of Computer Science and Engineering University of North Texas. Email: smohanty@cse.unt.edu

Acknowledgment: This work is partially supported by NSF award number 0702361.

# **Summary and Conclusions**

- We present a novel parasitic and process variation aware methodology for performance optimization of radio frequency (RF) circuit components.

- The proposed methodology performs the multiple iterations automatically on a parasitic parameterized netlist derived from the layout. The manual iteration is reduced to 1.

- The degradation in the oscillation frequency of an RF VCO due to parasitic and process variations has been narrowed down from 43.5% to 4.5%.

- Future work will address simultaneous optimization of frequency, linearity response, phase noise etc.

# Parasitic Aware Process Variation Tolerant Voltage Controlled Oscillator (VCO) Design

Dhruva Ghai, Saraju P. Mohanty and Elias Kougianos

University of North Texas, Denton, TX 76203.

Email: dvg0010@unt.edu, smohanty@unt.edu and eliask@unt.edu

## Abstract

- At nanoscale technologies, process variations have significant impact on circuit performance and need to be included in the design cycle. RLCK parasitics cause further performance degradations.

- We present a parasitic aware, process variation tolerant design methodology. A 90nm current starved VCO has been treated as case study.

- The oscillation frequency of the VCO is the objective function with area overhead as constraint. A degradation of 43.5% is observed when the RLCK parasitic extracted circuit is subjected to worst case process variation. After a single physical design iteration, the oscillation frequency is within 4.5% of the target.

### **Introduction and Motivation**

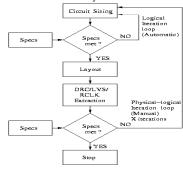

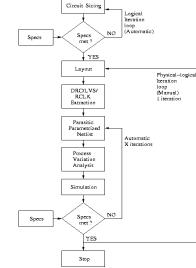

Standard RFIC design flows require multiple (X) manual iterations on the back-end layout to achieve parasitic closure between the front-end circuit and back-end layout:

The proposed methodology performs the multiple (X) iterations automatically on a parasitic parameterized netlist derived from the layout. The manual iteration is reduced to 1. To have a process variation robust design, process variation analysis is introduced in the design flow.

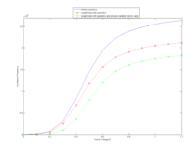

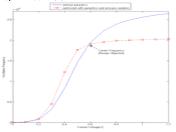

- Figure below shows the frequency-voltage characteristics of the VCO.

- Uppermost curve shows the characteristics for logical design. Oscillation frequency = 2GHz.

- Middle curve shows the characteristics for parasitic extracted layout. Discrepancy = 25%.

Bottom curve shows the characteristics for

- parasitic extracted layout subjected to *worst* case process variation. Oscillation frequency = 1.13GHz. Discrepancy = 43.5%.

# VCO Logical Design

Current starved VCO design performed using 90nm generic process. Target oscillation frequency (f0)= 2GHz.

# VCO Performance Optimization for Parasitics and Process Variations

• {V<sub>DD</sub>, V<sub>T,NMOS</sub>, V<sub>T,PMOS</sub>, T<sub>OX,NMOS</sub>, T<sub>OX,PMOS</sub>} chosen as parameters for process variation. • Parameters varied by +/-10% from their

nominal values. Worst case identified in which  $V_{DD}$  is reduced by 10%, and process parameters are increased by 10%. In this case, a 43.5% discrepancy is observed between the logical and physical design.

| Parameter           | Unoptimized | Unoptimized       | Optimized         |

|---------------------|-------------|-------------------|-------------------|

|                     | Physical    | Physical Design + | Physical Design + |

|                     | Design      | Process variation | Process Variation |

| frequency           | 1.56GHz     | 1.13GHz           | 1.91GHz           |

| discrepancy         | 25%         | 43.5%             | 4.5%              |

| $V_{DD}$            | 1.2V        | 1.08V             | 1.08V             |

|                     | (nominal)   | (-10%)            |                   |

| V <sub>T,NMOS</sub> | 0.1692662V  | 0.186193V         | 0.186193V         |

|                     | (nominal)   | (+10%)            |                   |

| $V_{T,PMOS}$        | -0.1359511V | -0.149546V        | -0.149546V        |

|                     | (nominal)   | (+10%)            |                   |

| $T_{ox,NMOS}$       | 2.33nm      | 2.563nm           | 2.563nm           |

|                     | (nominal)   | (+10%)            |                   |

| $T_{oz,PMOS}$       | 2.48nm      | 2.728nm           | 2.728nm           |

|                     | (nominal)   | (+10%)            |                   |

Parasitic-aware netlist from first layout is parameterized, and subjected to optimization loop in circuit simulator. {Wp, Lp, Wn, Ln, Wpcs, Lpcs, Wncs, Lncs} constitute set of design variables.

| Parameter | Varied<br>from | Varied<br>to | Optimized<br>Value |

|-----------|----------------|--------------|--------------------|

| $W_n$     | 200nm          | 500nm        | 415nm              |

| $W_P$     | 400nm          | $1 \mu m$    | 665nm              |

| $W_{ncs}$ | $1 \mu m$      | $5\mu m$     | $4 \mu m$          |

| $W_{pcs}$ | $5\mu m$       | $20 \mu m$   | $19 \mu m$         |

| Ĺ         | 100nm          | 110nm        | 100nm              |

Using optimized design variables: •Target  $f_0 \ge 2GHz$ .

Logical design f<sub>0</sub> = 1.95GHz.

Physical design f<sub>0</sub> in worst case process variation environment = 1.91

GHz. •Physical design  $f_0$  in nominal case process environment = 2.54 GHz.

Hence a final optimized layout with  $f_0$ = 1.91GHz under worst case process variation is obtained with only 1 manual (layout) iteration.

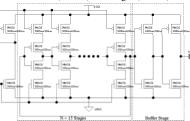

# VCO Physical Design

• Physical design carried out using a 90nm salicide 1.2V/ 2.5V 1 Poly 9 Metal process.

Full extraction including resistors (R), capacitors (C), inductors (L) and mutual inductors (K) is performed.

Multi-fingered transistors are laid out to minimize the area overhead.

| Parameter                    | Value                                          |

|------------------------------|------------------------------------------------|

| Technology                   | 90nm CMOS 1P 9M                                |

| Supply Voltage $(V_{DD})$    | 1.2V                                           |

| Oscillation frequency        | 2.54GHz                                        |

| (Nominal process)            |                                                |

| Process and supply variation | $V_T$ (+10%), $T_{ox}$ (+10%), $V_{DD}$ (-10%) |

| Oscillation frequency        | 1.91GHz                                        |

| (Worst-case process)         |                                                |

| Number of design variables   | $5(W_n, W_p, W_{ncs}, W_{pcs}, L)$             |

| Number of objectives         | $1 (f_0 \ge 2GHz)$                             |

Frequency-voltage characteristics of the optimized VCO

#### Conclusions

• We present a novel parasitic and process variation aware methodology for performance optimization of RF circuit components.

• The degradation in the oscillation frequency of an RF VCO due to parasitic and process variations has been narrowed down from 43.5% to 4.5%.

• Future work will address simultaneous optimization of frequency, linearity response, phase noise etc.

This work is partially supported by NSF award number 0702361.

VLSI Design and CAD Laboratory (VDCL) NORTH\*TEXAS