A Universal Voltage Level Converter for Multi-V<sub>DD</sub> Based Low-Power Nano-CMOS Systems-on-Chips (SoCs)

> Saraju P. Mohanty, S.T. Vadlamudi and E. Kougianos VLSI Design and CAD Laboratory (<u>www.vdcl.cse.unt.edu</u>) Dept. of Computer Science and Engineering University of North Texas <u>smohanty@cse.unt.edu</u>, <u>stv0009@unt.edu</u>, <u>eliask@unt.edu</u>

> > *Presented by Dhruva Ghai* University of North Texas

> > > dhruva@unt.edu

Mohanty, Vadlamudi and Kougianos 1

Agenda

#### □ Introduction

- □ Related research works

- Design of ULC

- □ Simulation results at 90nm technology

- □ Characterization of ULC

- Custom layout design at 90nm technology

- Conclusion and future works

# Introduction

- Power dissipation reduction has become a major design issue for VLSI design at nano-scale technologies.

- □ Sources of power dissipation

- Dynamic power

- Static power

- Power dissipation due to leakage currents

$$P_{total} = s * C * V_{DD}^{2} * f + I_{sc} * V_{DD} + I_{leakage} * V_{DD}$$

# Techniques for power dissipation reduction

Reducing the supply voltage

Transistor sizing

Multiple threshold voltages

Multi-voltage supply systems

# Multi- $V_{DD}$ supply system

- Multiple voltage supply systems are one of the most efficient methods to reduce power dissipation

- The system is divided into voltage islands operating at different supply voltages

- Level converters are used as interface between to voltage islands

- Level converter: A circuit which changes the voltage level at its input to another level at the output side is known as a level converter

#### Need for level converter

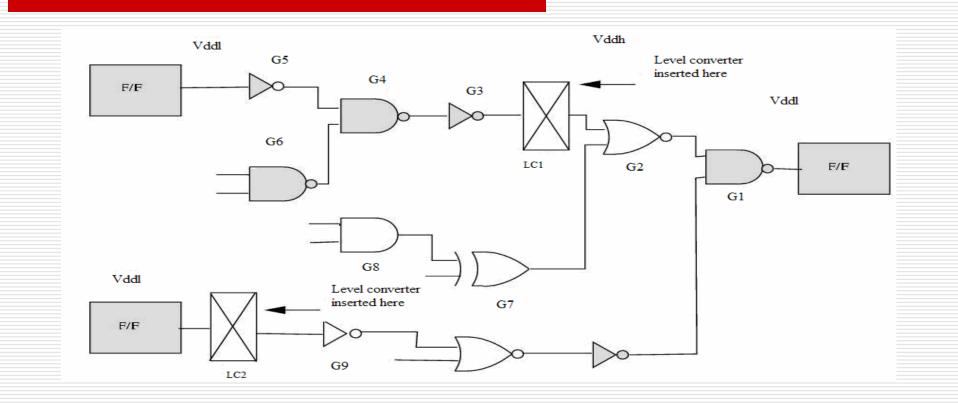

Block diagram of a multi-voltage supply system demonstrating the need for level converter

NASA VLSI 2007

#### UNIVERSITY OF NORTH\*TEXAS

## Need for a level converter

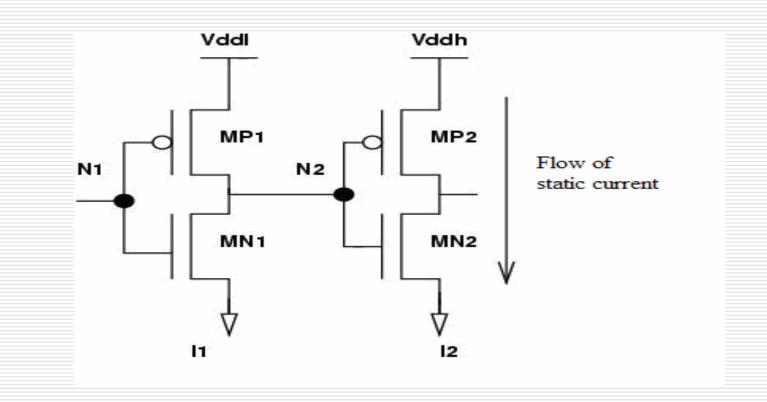

Direct connection between two inverters demonstrating the need for level converter

Mohanty, Vadlamudi and Kougianos 7

# Related research works

- Clustered voltage scaling : Allows insertion of level converters at the interface of cells at different voltages

- Extended clustered voltage scaling : Allows insertion of level converters between any gates, wherever level conversion is required

### Related research work (*contd.*.)

| Year | Technol<br>ogy                       | Type of<br>circuit                                                                                                                                       | Design approach                                                                                                                                                                                      | Power<br>consum<br>ption                                                                                                                                                                                                                                                                                                                                                                                                            | Delay                                                                                                             |

|------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 2004 | 0.13mm                               | Level up<br>converter                                                                                                                                    | Level converting flip flops<br>LCFF                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 287 ps                                                                                                            |

| 1999 | 0.13mm                               | Level up<br>converter                                                                                                                                    | DCVS and Keeper<br>transistor                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                   |

| 2001 | 0.35mm                               | Level up<br>Converter                                                                                                                                    | Symmetrical Dual Cascode<br>Voltage Switch                                                                                                                                                           | 220.57<br>mW                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                   |

| 2006 | 0.1mm                                | Level up<br>Converter                                                                                                                                    | Keeper transistor in pass<br>transistor logic                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                   |

| 2000 | 0.14mm                               | Level down converter                                                                                                                                     | Differential input pair operation                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                   |

| 2003 | 0.1mm                                | Level up<br>converter                                                                                                                                    | Dynamic Level Converter                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                     | <<br>120ps                                                                                                        |

|      | 2004<br>1999<br>2001<br>2006<br>2000 | ogy           2004         0.13mm           1999         0.13mm           2001         0.35mm           2006         0.1mm           2000         0.14mm | ogycircuit20040.13mmLevel up<br>converter19990.13mmLevel up<br>converter20010.35mmLevel up<br>Converter20060.1mmLevel up<br>Converter20000.14mmLevel down<br>converter20030.1mmLevel up<br>Converter | ogycircuit20040.13mmLevel up<br>converterLevel converting flip flops<br>LCFF19990.13mmLevel up<br>converterDCVS and Keeper<br>transistor20010.35mmLevel up<br>ConverterSymmetrical Dual Cascode<br>Voltage Switch20060.1mmLevel up<br>ConverterKeeper transistor in pass<br>transistor logic20000.14mmLevel down<br>ConverterDifferential input pair<br>operation20030.1mmLevel up<br>ConverterDifferential input pair<br>operation | ogycircuitconsum<br>ption20040.13mmLevel up<br>converterLevel converting flip flops<br>LCFF19990.13mmLevel up<br> |

**ORTH\*TEXAS**

NASA VLSI 2007

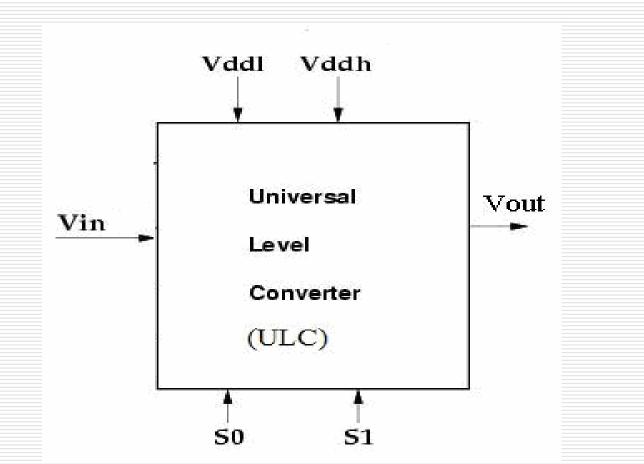

# Universal Level Converter

□ Level up conversion

□ Level down conversion

Blocking of signal

Passing signal

Mohanty, Vadlamudi and Kougianos 10

# Operations of ULC

| Select | signal | Type of       |

|--------|--------|---------------|

| sO     | s1     | operation     |

| 0      | 0      | Passing       |

|        |        | operation     |

| 0      | 1      | Blocking      |

|        |        | operation     |

| 1      | 0      | Down          |

|        |        | conversion    |

| 1      | 1      | Up conversion |

UNIVERSITY OF ORTH\*TEXAS

NASA VLSI 2007

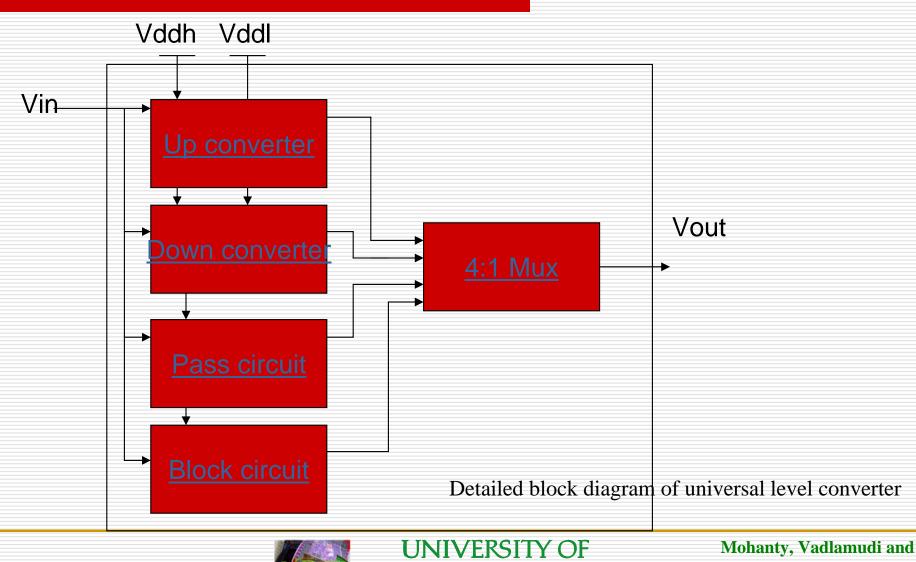

# Design of Universal level converter

High Level view of Universal level converter proposed

NASA VLSI 2007

(Contd..)

**NORTH\*TEXAS**

NASA VLSI 2007

Kougianos 13

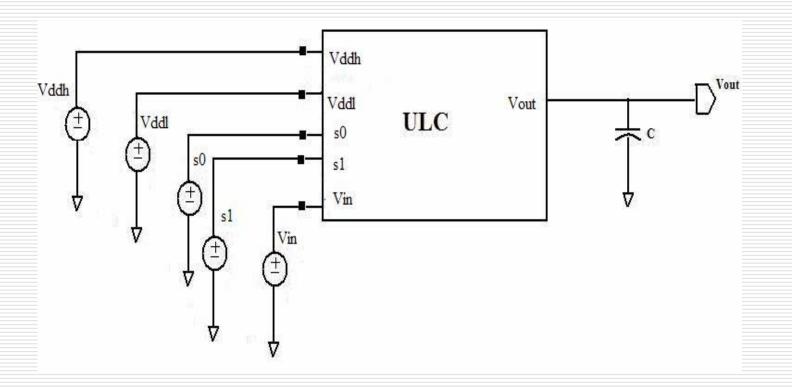

## Simulation test bench

Simulation test bench of universal level converter

NASA VLSI 2007

# Simulation results of ULC

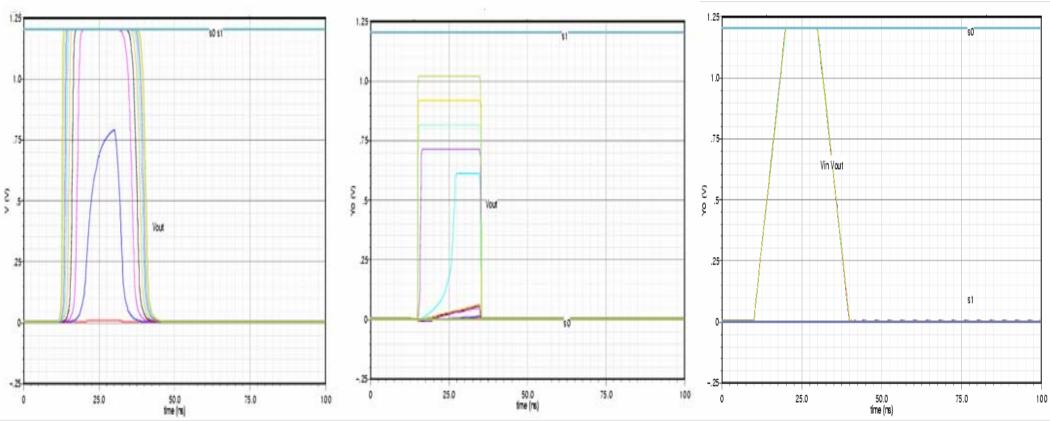

Simulation results for ULC showing the output waveforms in all modes of operation

**UNIVERSITY OF**

$\star$

ƘAS™

NASA VLSI 2007

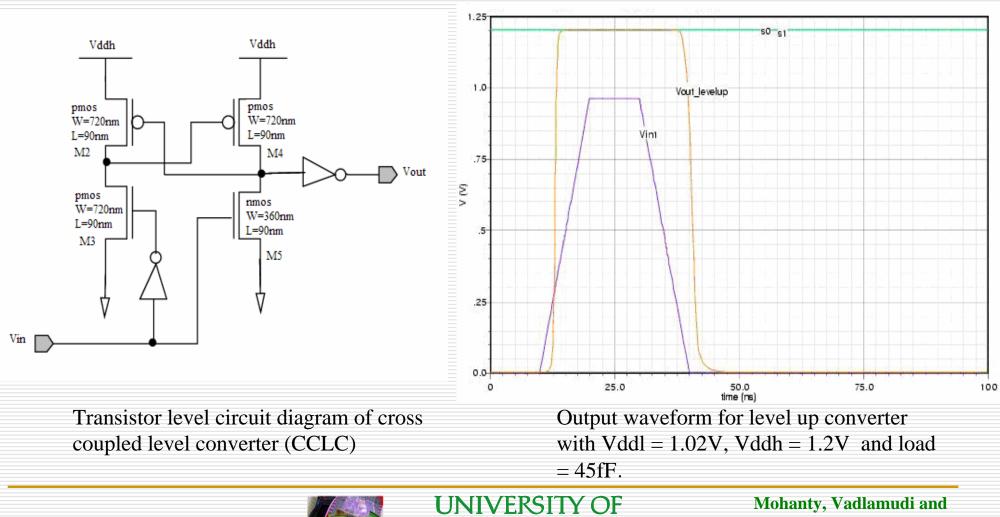

#### Level up converter

$\star$

**(AS**<sup>™</sup>

**NASA VLSI 2007**

Kougianos 16

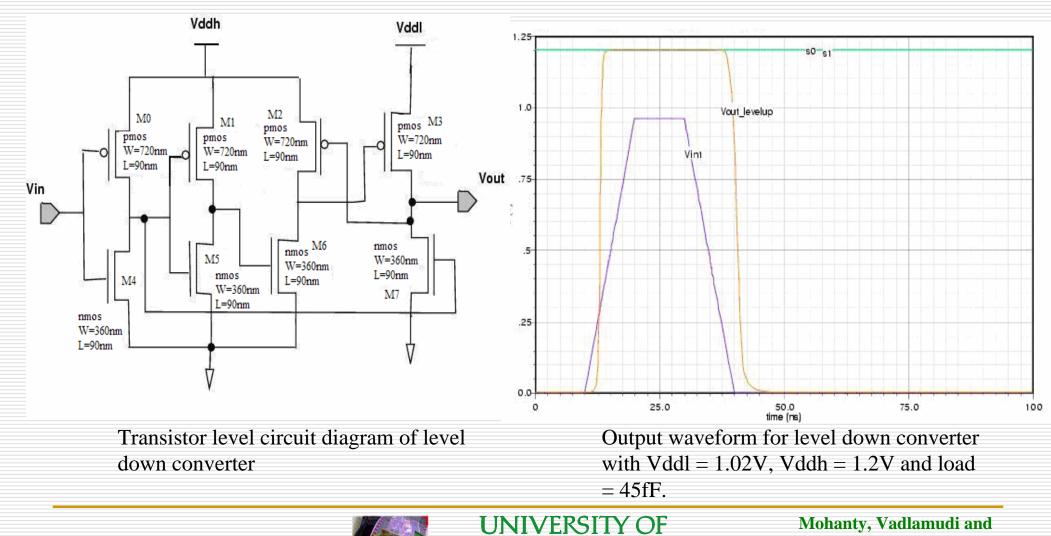

#### Level down converter

**TH\*TE**

XAS™

**NASA VLSI 2007**

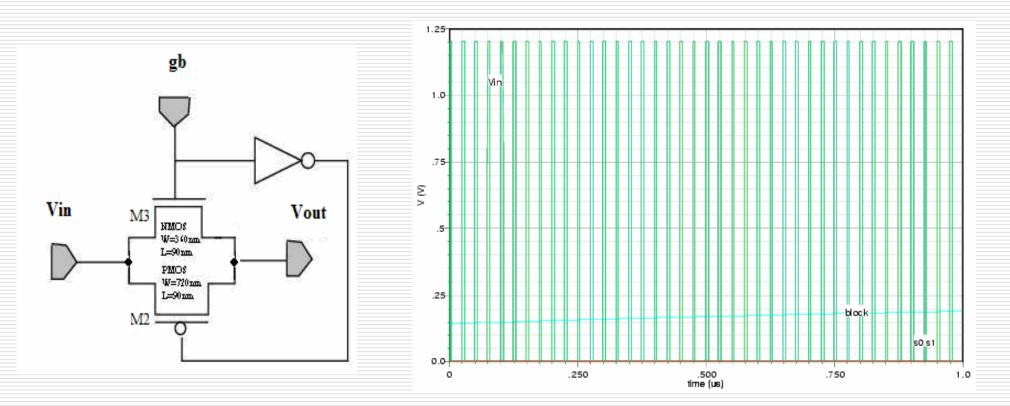

# Level blocking circuit

**UNIVERSITY OF**

**(AS**<sup>™</sup>

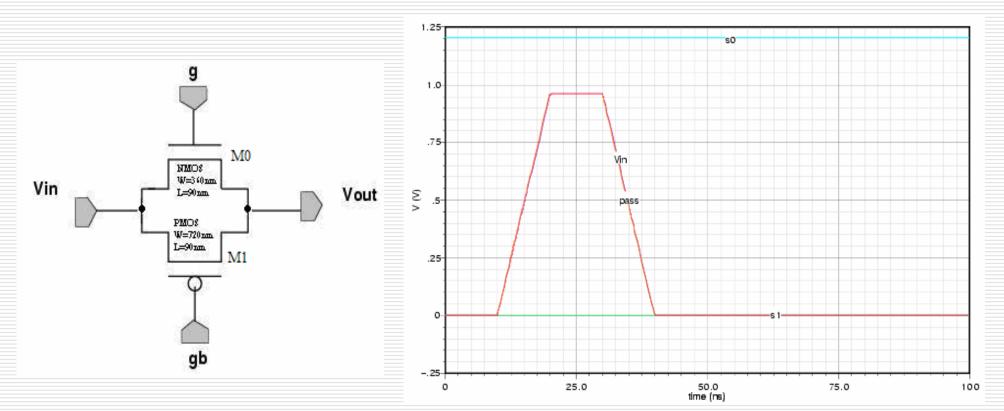

Transistor level circuit diagram of blocking circuit

Output waveform for level up converter with Vddl = 1.02V, Vddh = 1.2V and load = 45fF.

NASA VLSI 2007

#### Pass circuit

**UNIVERSITY OF**

**HTEXAS**

Transistor level circuit diagram of pass circuit

Output waveform for pass circuit with Vddl = 1.02V, Vddh = 1.2V and load = 45fF.

#### NASA VLSI 2007

# Characterization of ULC

Power analysis

#### Load analysis

Mohanty, Vadlamudi and Kougianos 20

#### Parametric analysis

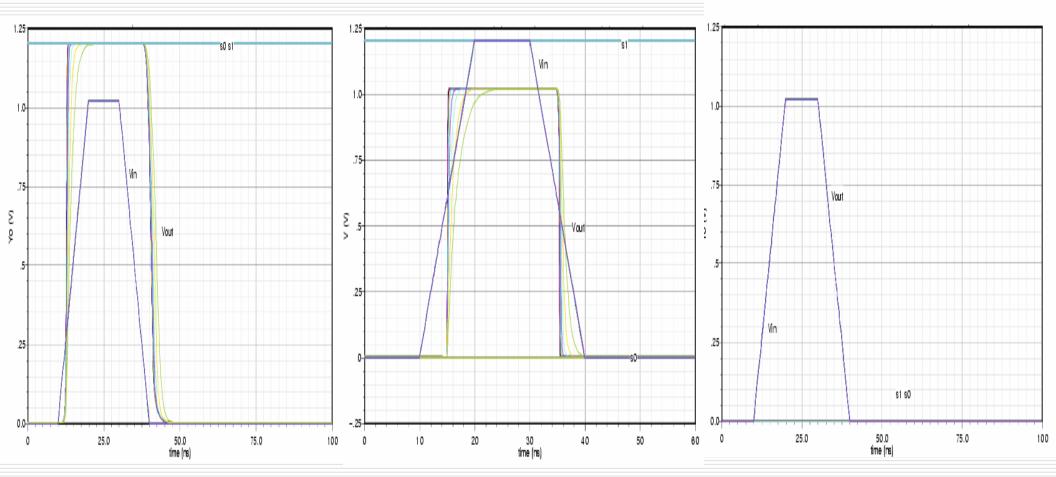

Output waveforms of parametric analysis of ULC where Vddl is varied from 0.1V to 1.02V and Vddh is kept constant at 1.2V

NASA VLSI 2007

#### UNIVERSITY OF NORTH\*TEXAS

#### Power analysis

#### $\Box$ Total average power of ULC = 26.928 $\mu$ W

Mohanty, Vadlamudi and Kougianos 22

# Load analysis

**UNIVERSITY OF**

**RTH**\***TEXAS**<sup>™</sup>

Output waveforms of load analysis of ULC where load is varied from 1fF to 200fF.

NASA VLSI 2007

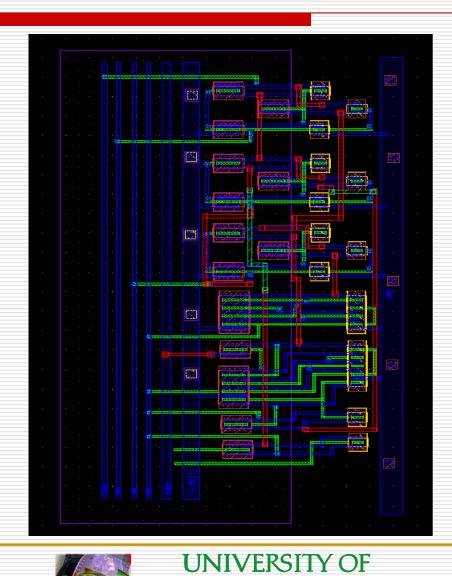

# Custom layout design of ULC

- Layout design of ULC is created at 90nm technology

- $\square$  PMOS W=1µm and L= 100nm

- $\square$  NMOS W= 500nm and L= 100nm

- □ 90nm general process design kit

- Verified using the assuraDRC.rul during DRC check

#### Universal level converter

**RTH**\***TEXAS**<sup>™</sup>

NASA VLSI 2007

# Conclusion

- Proposed a unique level converter design capable of four level converting operations

- Characterized the proposed design using parametric, power and load analysis at 90nm technology

- ULC consumes has an average power reduction of about 85-97% and is capable of producing stable output even under varying load from 1fF -200fF and at voltages as low as 0.6V

#### Future works

- Proposed design can be improved at schematic as well as layout level. Post layout simulation results to be presented.

- The technology can be further scaled down to 45nm.

- □ ULC design could be improved in the delay aspect.