## SI Design and CAD Research at University of North Texas

### Associated Laboratory VLSI Design and CAD Laboratory http://www.vdcl.cse.unt.edu

Saraju P. Mohanty Dept of Computer Science and Engineering University of North Texas smohanty@cs.unt.edu http://www.cs.unt.edu/~smohanty/

### **Outline of the Talk**

About VDCL

Research Activity

Publications

Opportunities for Masters and Ph.D.

- Established in August 2004

- Mission:

- to carry out research in low power VLSI design

- to prepare next generation CAD tools for automatic design

- One Faculty, one associated Faculty, and six student members.

- Located at F233.

- State-of-art research infrastructure include Sun Fire server, Dual-Xeon Servers, Sun Workstations, Linux Workstations and Tera Bytes of storage.

- Licensed and free CAD tools available.

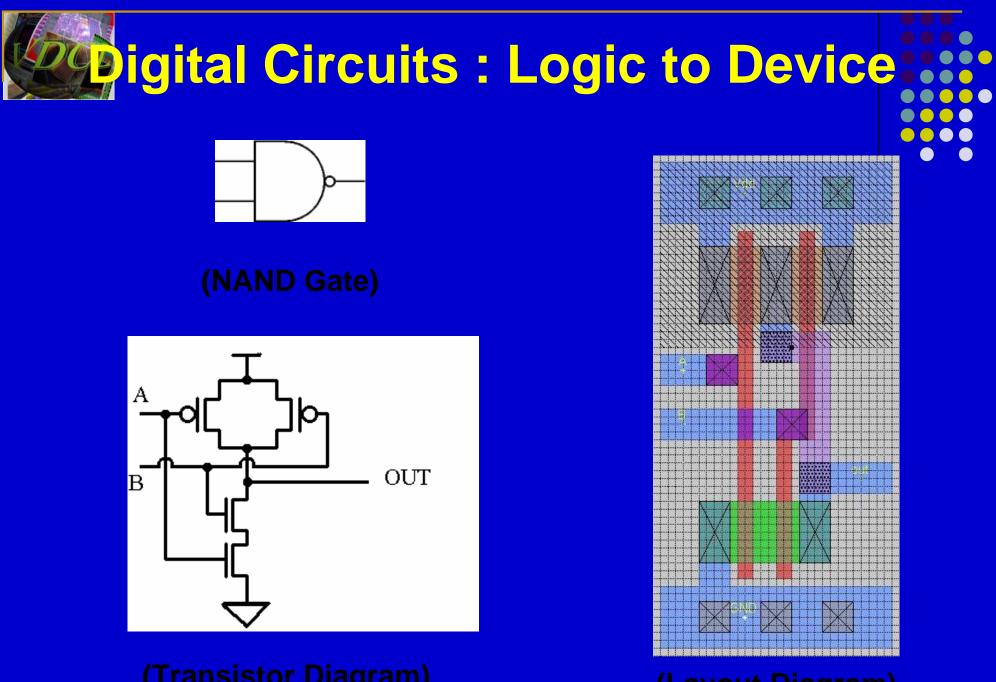

Almost the entire industry today is driven by CMOS

#### (2) Sun UltraSpare

#### (3) PentiumPro

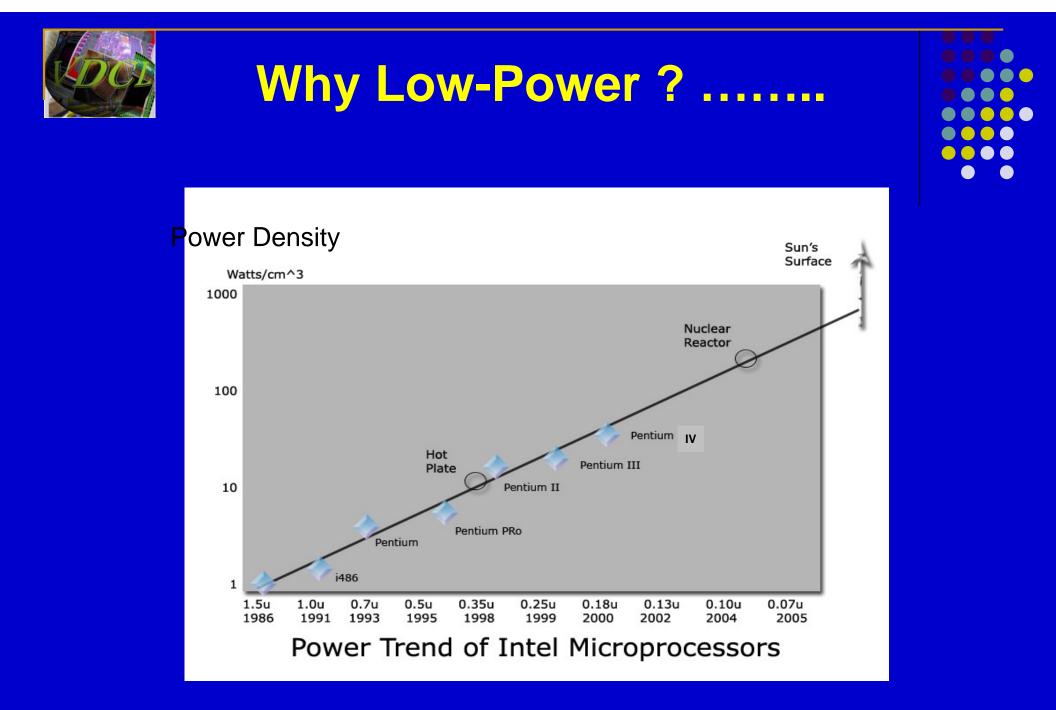

## Technology: Highest Growth in History

- 1958: First integrated circuit

- Flip-flop using two transistors

- Built by Jack Kilby at Texas Instruments

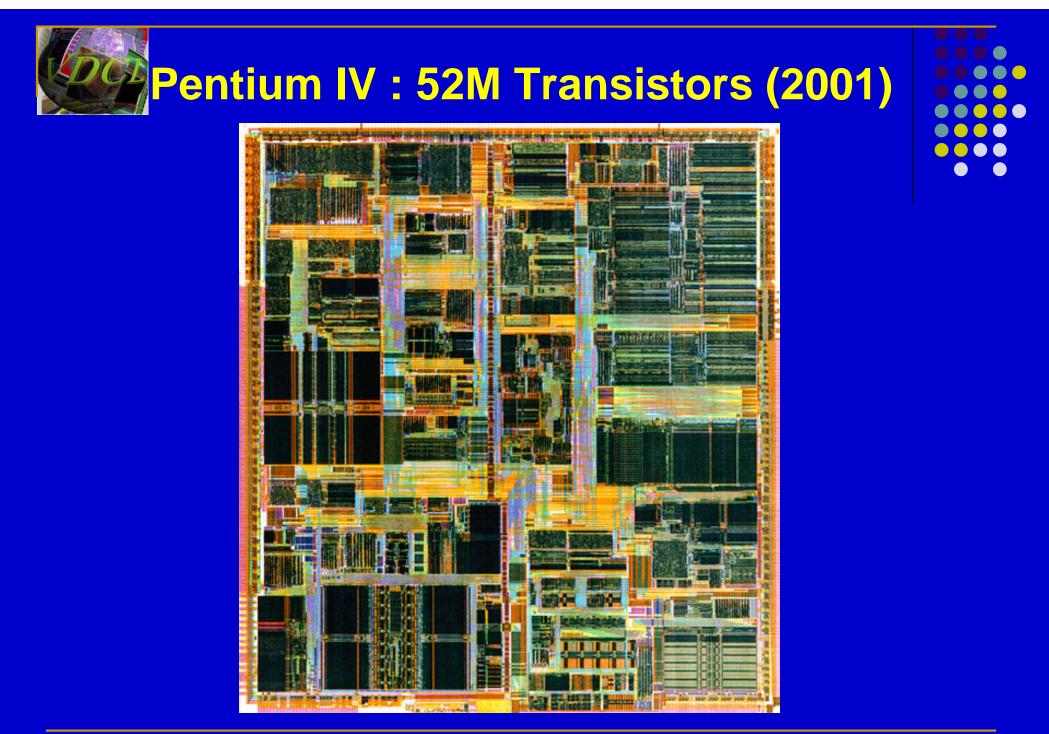

- **2003**

- Intel Pentium 4 μprocessor (55 million transistors)

- 512 Mbit DRAM (> 0.5 billion transistors)

- 53% compound annual growth rate over 45 years

- No other technology has grown so fast so long

- Driven by miniaturization of transistors

- Smaller is cheaper, faster, lower in power!

- Revolutionary effects on society

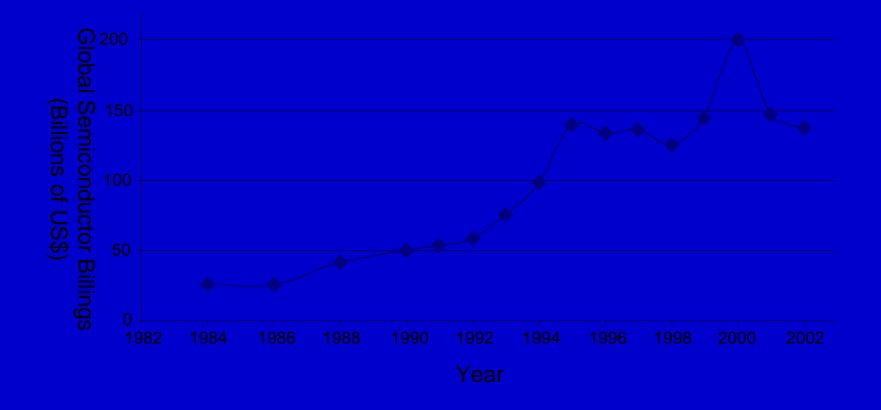

### **VLSI Industry : Annual Sales**

# 10<sup>18</sup> transistors manufactured in 2003 100 million for every human on the planet

### **Research Interests**

Synthesis and Optimization for Low Power

- Power Aware System Design

- VLSI Architecture for Security and Copyright Protection

- CAD and Modeling for Nanoscale VLSI Circuits

### **Research Interests ...**

- Synthesis and Optimization for Low Power

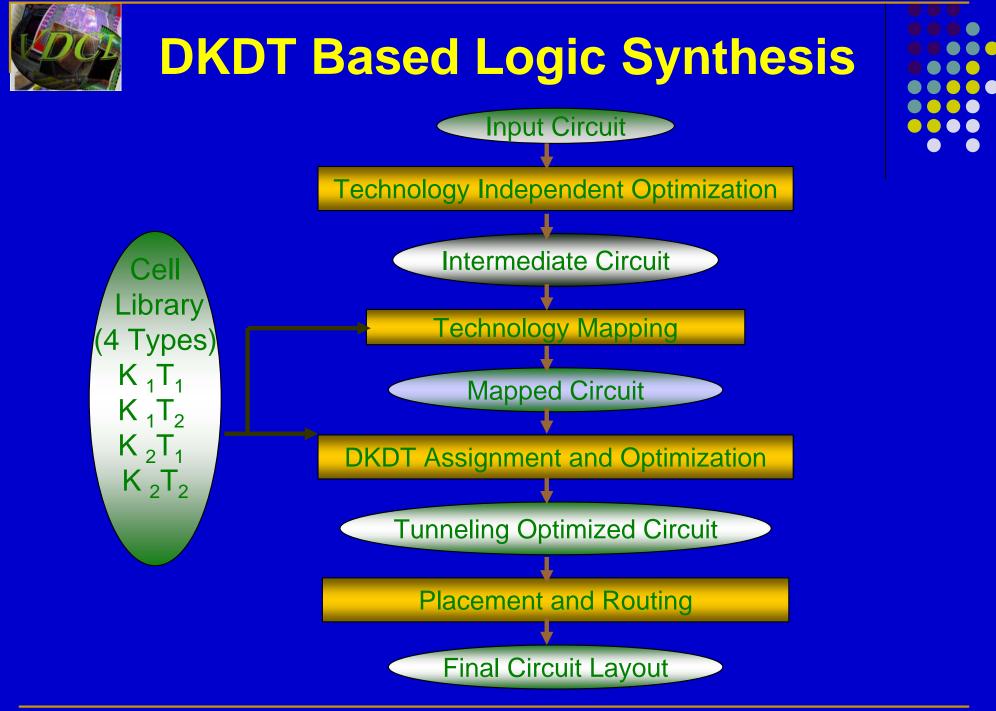

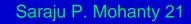

- Vary supply voltage, clock frequency, switching activity and capacitance, physical parameter through various phases of the synthesis process while considering their interactions and trade-offs.

- Power Aware System Design

- Aim is to provide a low power, high performance architecture followed by its VLSI implementation for different applications, such as image and video processing, and wireless system

VLSI Architecture for Security and Copyright

Protection

- Goal is to develop architectures to perform compression, encryption, watermarking and scrambling in a common hardware.

- CAD and Modeling for Nanoscale VLSI Circuits

- Plan is to develop models for fast characterization of architectural and logic cells made of nonclassical CMOS.

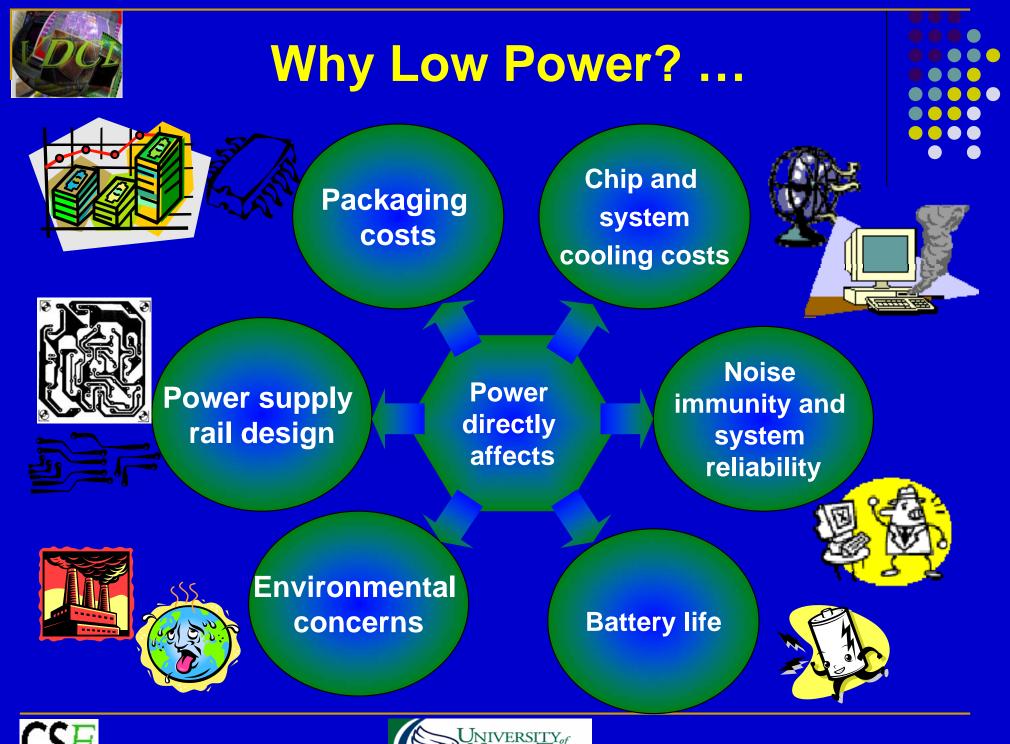

### Why Low Power?

Major Motivation

Reducing Power Consumption

Increasing Battery Life

Making Portable Devices Really Portable...

Source: Weste and Harris 2005

$\checkmark$

$\checkmark$

$\checkmark$

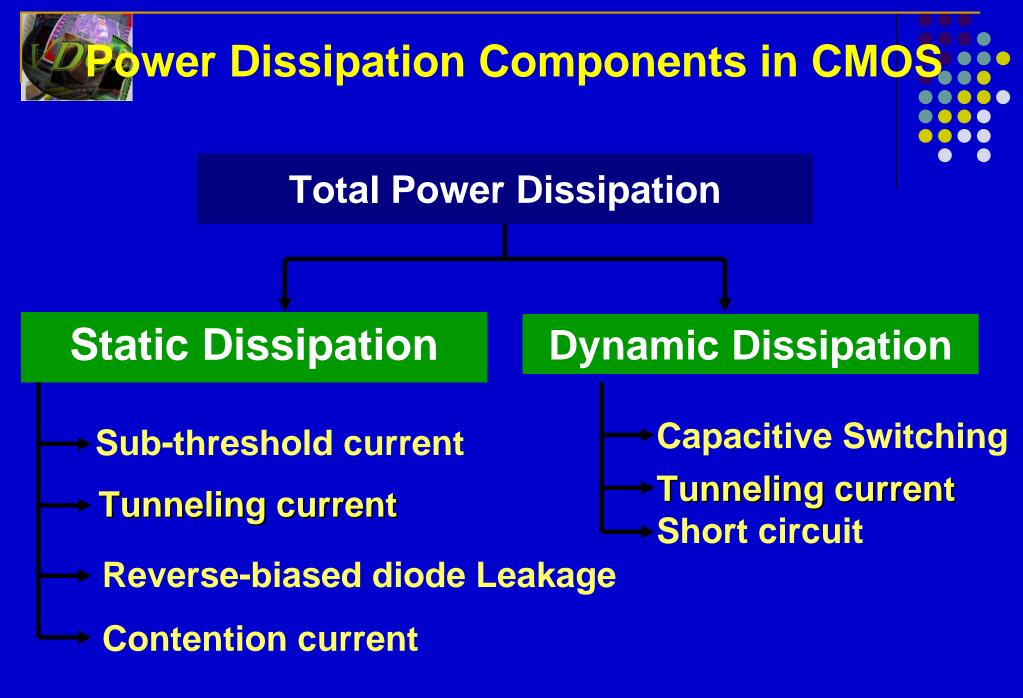

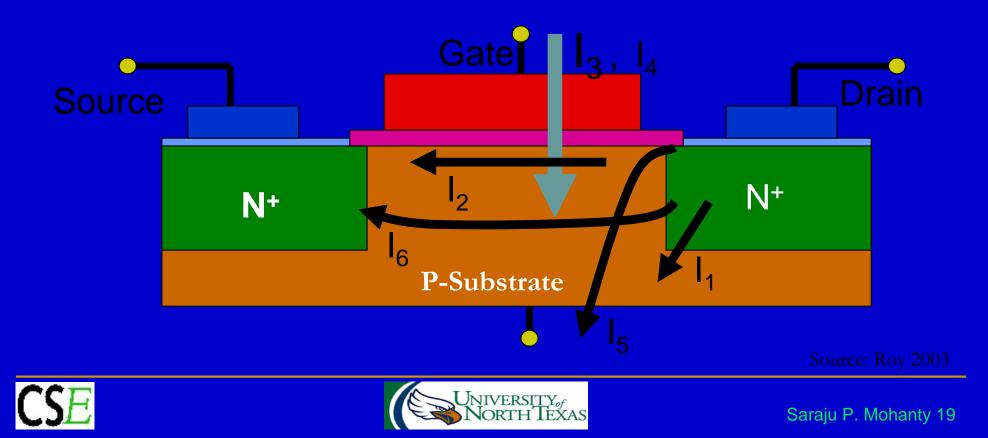

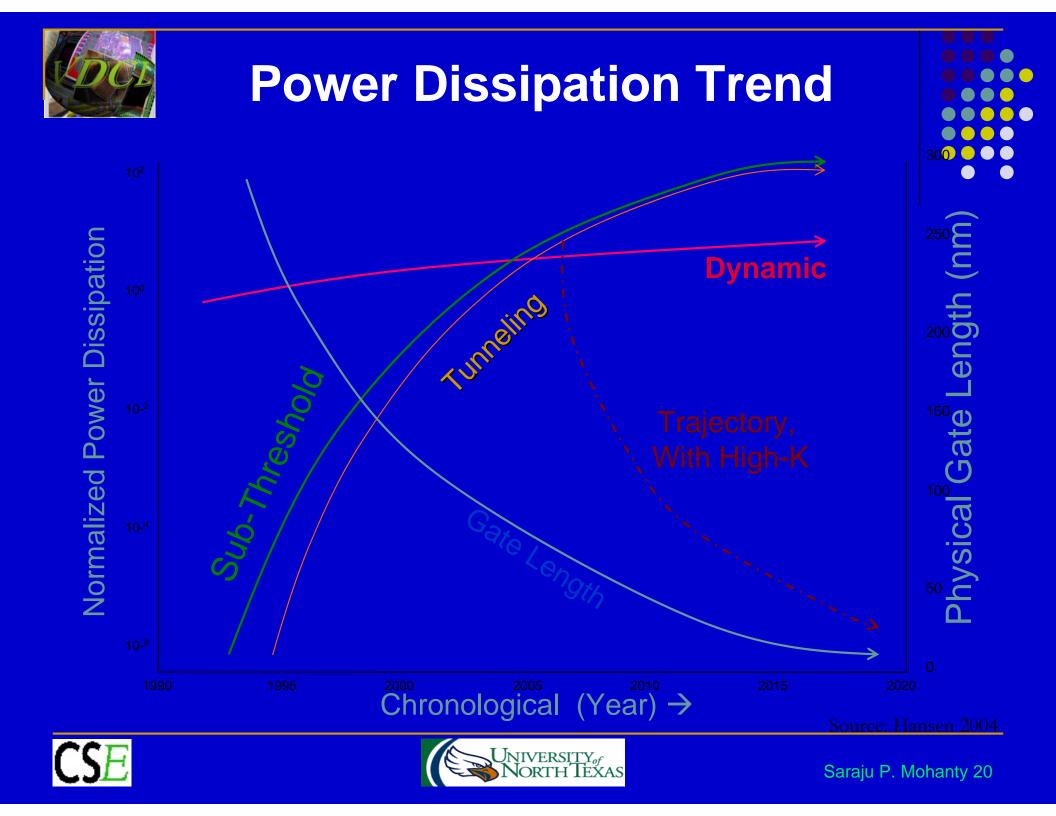

### Leakages in Nanometer CMOS

- $I_1$ : reverse bias pn junction (both ON & OFF)  $\checkmark$  $\checkmark$

- I<sub>2</sub>: subthreshold leakage (OFF)

- I<sub>3</sub>: oxide tunneling current (both ON & OFF)

- $I_{A}$ : gate current due to hot carrier injection (both ON & OFF)

- $I_5$ : gate induced drain leakage (OFF)

- I<sub>6</sub>: channel punch through current (OFF)  $\checkmark$

NIVERSITY<sub>of</sub>

### **NOTE:** DKDT has no time penalty.

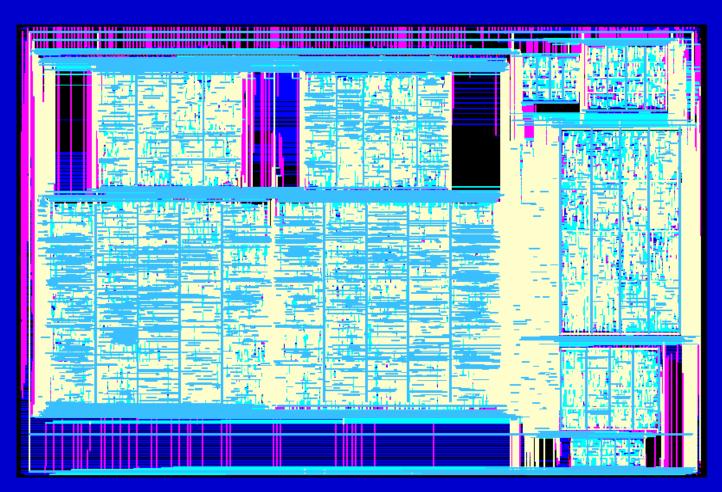

### **Chip: Statistics**

Technology: TSMC 0.25 µ Total Area : 16.2 sq mm Dual Clocks: 280 MHz and 70 MHz Dual Voltages: 2.5V and 1.5V No. of Transistors: 1.4 million Power Consumption: 0.3 mW

### **Our Publication Statistics**

### •Summary:

- 6 ACM/IEEE transactions accepted and several in pipeline

- 29 peer reviewed IEEE/ACM conference papers

### Selected List:

- S. P. Mohanty and N. Ranganathan, "Simultaneous Peak and Average Power Minimization during Datapath Scheduling", *IEEE Transactions on Circuits and Systems Part I (TCAS-I), Vol. 52, No. 6, June 2005, pp. 1157-1165.*

- S. P. Mohanty and N. Ranganathan, "Energy Efficient Datapath Scheduling using Multiple Voltages and Dynamic Clocking", ACM Transactions on Design Automation of Electronic Systems (TODAES), Vol. 10, No. 2, April 2005, pp. 330-353.

- S. P. Mohanty, N. Ranganathan, and R. K. Namballa, "A VLSI Architecture for Visible Watermarking in a Secure Still Digital Camera (S^2DC) Design", *IEEE Transactions on Very Large Scale Integration Systems (TVLSI)*, Vol. 13, No. 7, July 2005, pp. 808-818.

- S. P. Mohanty and N. Ranganathan, "A Framework for Energy and Transient Power Reduction during Behavioral Synthesis", *IEEE Transactions on VLSI Systems (TVLSI)*, Vol. 12, No. 6, June 2004, pp. 562-572.

### Ph. D. in Computer Science

### Background or through course:

- CMOS VLSI

- VLSI CAD

- Algorithms

- Graph Theory

- Optimization Techniques

- Architecture

- Can focus on:

- Any of the four research interests mentioned

### **MS in Computer Science**

### Background or through course:

- CMOS VLSI

- VLSI CAD

- Algorithms

- Graph Theory

- Optimization Techniques

- Can focus on:

- CAD and Optimization for VLSI

### **MS in Computer Engineering**

### Background or through course:

- CMOS VLSI

- Semiconductor Physics

- Algorithms

- Advanced VLSI Systems

- Can focus on:

- Any of the four research interests mentioned

### **Advantages of Thesis Option**

Less number of credit hours

Chance of getting degree in 3 full semesters

Chances of getting assistantship is higher

Improves credibility of your masters degree

Higher chances of getting better job

More bargaining power for salary

# Thank You !!!